# PACKAGE 2 LOW/HIGH RESOLUTION MODIFICATION PROCEDURE

#### CONTENTS

MOTHER BOARD PLUS WIRE RAM BOARD, WHICH CONTAINS VIDEO AND USER RAM.

### COMMENTS

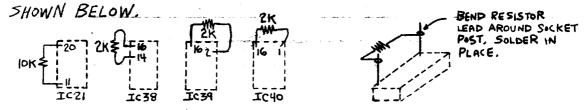

IT IS ASSUMED THE USER OF THIS PROCEDURE HAS A COPY OF THE BALLY SERVICE MANUAL PA-1. BEGINNING EXPERIMENTERS IN DIGITAL ELECTRONICS SHOULD NOT ATTEMPT THIS UPGRADE. SEVERAL UNUSED GATE INPUTS ARE SHOWN WIRED TO +5V VIA A lok CURRENT LIMITING RESISTOR ALLOWING TTL CHIPS TO BE OCCASIONALLY SUBSTITUTED IN LIEU OF LSTTL CHIPS. IF ONLY LSTTL CHIPS WILL BE UTILIZED, THEN WIRE THE UNUSED INPUTS DIRECTLY TO +5V (NO RESISTOR). NUMBERS FOLLOWING PROCEDURE STATEMENTS INDICATE A REFERENCE SHOULD BE MADE TO THE NOTE NUMBERS WHICH ARE LISTED FOLLOWING THE PROCEDURE.

TWO LOW RESOLUTION DEMOS AND A HIGH RESOLUTION DEMO, FOR TESTING PURPOSES, ARE AVAILABLE ON CASSETTE TAPE. MAIL THE REQUEST FOR THE DEMOS ALONG WITH \$7.00, TO COVER THE COST OF THE TAPE, POSTAGE AND PACKAGING, TO:

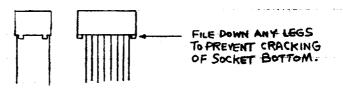

MICHAEL C. MATTÉ 8605 W. DOUGLAS AVE. MILWAUKEE, WI. 53225

REASONABLE QUESTIONS CONCÉRNING THE UPGRADE MAY ALSO BE MAILED TO THE ABOVE ADDRESS. A SELF-ADDRESSED STAMPED ENVELOPE WILL PRODUCE A REPLY TO ANY QUESTION(S).

# LOW/HIGH RESOLUTION MODIFICATION

### PROCEDURE

19 DISASSEMBLE MOTHER BOARD FROM BALLY ARCADE. 19

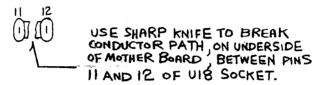

2 DISCONNECT PINS 11 AND 12 OF CUSTOM DATA CHIP U18 FROM EACH OTHER. CONFIRM DISCONNECTION WITH OHM-METER.

3 DISCONNECT PIN II OF CUSTOM DATA CHIP UIS FROM GROUND.

CONFIRM DISCONNECTION WITH OHM-METER. USE OHM-METER TO CONFIRM PIN 1 OF UIS IS NOT DISCONNECTED FROM GROUND.

- 4) THE MOTHER BOARD SHOULD STILL OPERATE AT THIS POINT. SEE NOTES 1-3.

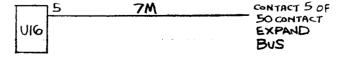

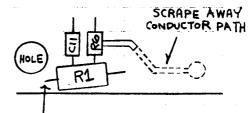

- B REMOVE SIX IKS PULL-UP RESISTORS, USED FOR VIDEO RAM ADDRESS LINES AO-AS, FROM MOTHER BOARD. FIVE OF THE RESISTORS ARE NEAR RESISTOR R1. THE SIXTH RESISTOR IS BETWEEN CAPACITORS (78 AND (79.

- @ REPLACE RESISTOR RIY ON MOTHER BOARD WITH A JUMPER WIRE. CONFIRM WITH OHM-METER THE FOLLOWING CONNECTION:

REMOVE CAPACITOR CI8 FROM MOTHER BOARD.

THE MOTHER BOARD SHOULD STILL OPERATE AT THIS POINT. SEE NOTES 1-3.

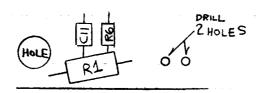

DRILL SMALL HOLE. TWIST TWO PIECES OF #30 WRAP-PING WIRE TO GETHER. ON BOTTOM SIDE OF MOTHER BOARD, SOLDER ONE END OF WIRE TO R1 AND THE OTHER END OF WIRE SOLDER TO VOLTAGE REGULATOR VR2 INPUT TERMINAL.

BEFORE

AFTER

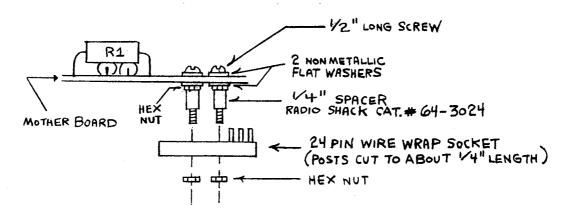

9 MOUNT 24 PIN WIRE WRAP SOCKET ON MOTHER BOARD.

- © CUT OUT RECTANGULAR HOLE IN BOTTOM PLASTIC CABINET, METAL AND PAPER SHIELDING SO MOTHER BOARD (AN BE PLACED IN ITS NORMAL POSITION ON CABINET BOTTOM.

- 1) THE MOTHER BOARD SHOULD STILL OPERATE AT THIS POINT. SEE NOTES 1-3.

- (2) REMOVE THE 24PIN WIRE WRAP SOCKET FROM MOTHER BOARD.

REMOVE CHIP U23 (DM81LS95) AND EIGHT VIDEO RAM CHIPS

U24-U31 FROM MOTHER BOARD. CLEAN UP AREAS ON

MOTHER BOARD TOUCHED BY SOLDERING IRON AND CHECK FOR SHORTS.

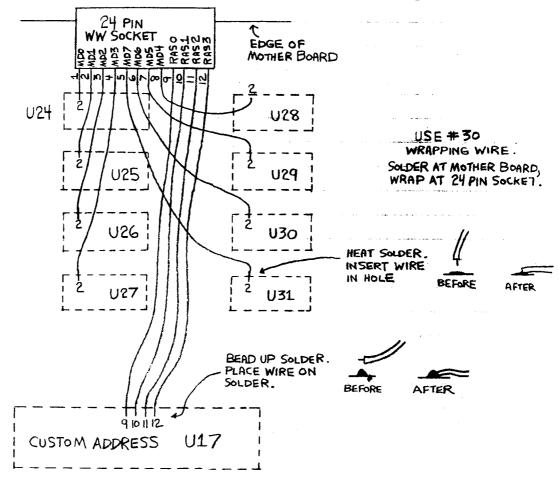

13 WIRE FROM BOTTOM OF MOTHER BOARD TO 24 PIN WIRE WRAP SOCKET THE DATA LINES MOO-MOT AND LINES RASO-RASS.

USE OHM-METER TO CONFIRM CONNECTIONS.

| CUSTOM<br>PATA<br>UIS    | 28<br>30<br>32<br>34<br>37<br>39<br>3<br>5 | MD0<br>MD1<br>MD2<br>MD3<br>MD4<br>MD5<br>MD6<br>MD7 | 12348795 | 24 PIN<br>WW<br>Socket |

|--------------------------|--------------------------------------------|------------------------------------------------------|----------|------------------------|

| CUSTOM<br>ADDRESS<br>U17 | 10 11                                      | Ras o<br>Ras I<br>Ras 2<br>Ras 3                     | 9 10 11  |                        |

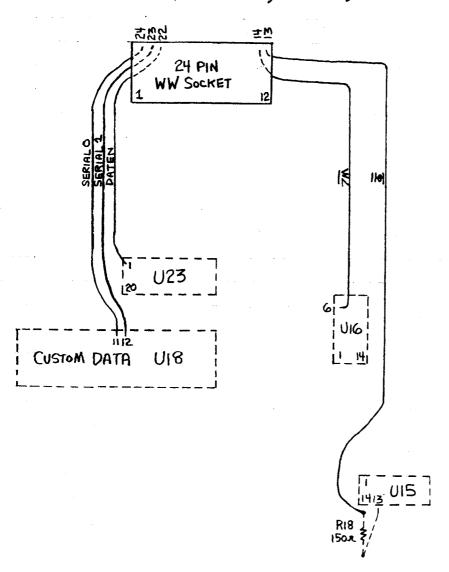

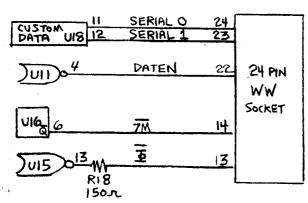

WWIRE FROM BOTTOM OF MOTHER BOARD TO 24 PIN WIRE WRAP SOCKET THE LINES DATEN, SERIAL 1, SERIAL 0, \$\overline{\Pi}\$ AND \$\overline{\TM}\$.

USE OHM-METER TO CONFIRM CONNECTIONS.

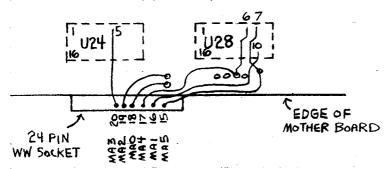

15 WIRE FROM TOP OF MOTHER BOARD TO 24 PIN WIRE WRAP SOCKET THE ADDRESS LINES MAO-MAS.

USE OHM-METER TO CONFIRM CONNECTIONS.

|     | 15 | MAO | 181 |                        |

|-----|----|-----|-----|------------------------|

| U20 | 7  | MAI | 16  | 24 PIN<br>WW<br>SOCKET |

|     | 5  | MAZ | 19  |                        |

|     | 2  | MAS | 20  |                        |

|     | 12 | MAY | 17  |                        |

| 1   | 2  | MA5 | 15  |                        |

| 1   |    |     |     |                        |

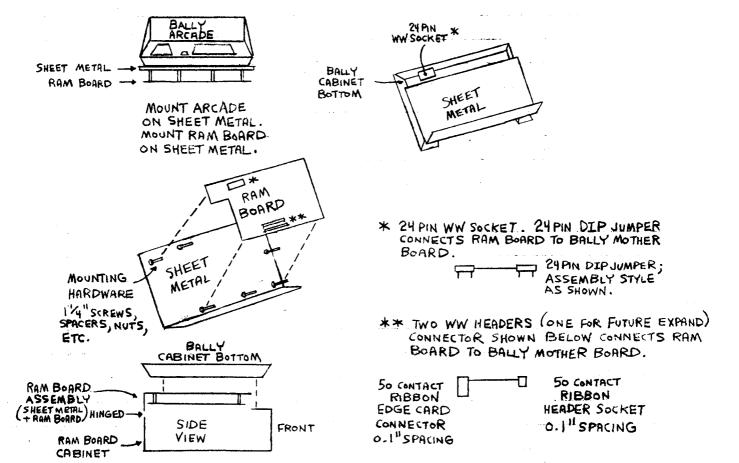

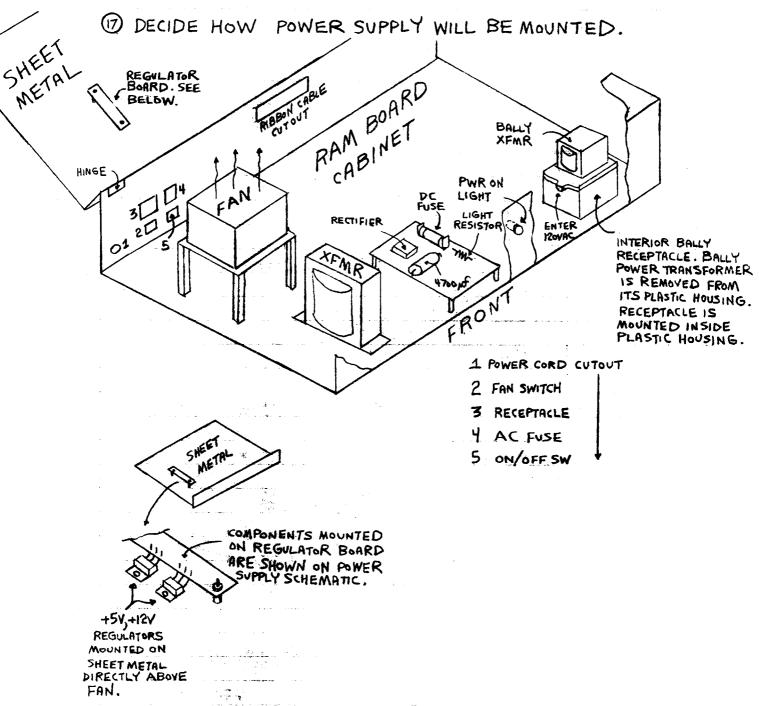

@ DECIDE HOW RAM BOARD WILL BE MOUNTED. 5

(ABINET AND SHEET METAL. CUT RAM BOARD (VECTORBORD 169P84WE) TO SIZE. MOUNT RAM BOARD AND BALLY (ABINET TO SHEET METAL. MOUNT THAT ASSEMBLY TO RAM BOARD (ABINET CHECKING FOR CLEARANCES. CHECK CLEARANCES WITH RIBBON CONNECTORS DESCRIBED IN (CONNECTED FROM MOTHER BOARD TO RAM BOARD.

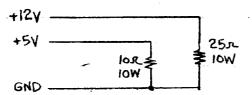

19 WIRE THE POWER SUPPLY. TEST THE +5V AND +12V DC SUPPLIES USING A DC VOLTMETER AND 1/2 AMP LOAD.

DESIGNER'S VOLTMETER READ 4.5VDC ACROSS JOJ RESISTOR AND 10.5VDC ACROSS 25% RESISTOR AFTER 30 MINUTES OF OPERATION.

TEST THE TWO 120VAC RECEPTACLES USING A 120VAC PORTABLE RADIO.

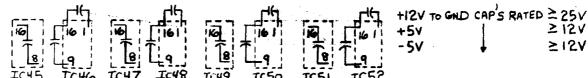

MOUNT THE FIRST BANK OF VIDEO RAM (SOCKETS IC 45-1052). 6,7 WIRE LINES VWE, VRAS, CASO, MAO-MAS, AG, -5v, +12v, +5V AND GND OF FIRST BANK. MOUNT SOCKETS IC36-IC44, IC31 AND 24 PIN RIBBON SOCKET. 6,7 WIRE THE +5V POSTS TOGETHER AND THE GND POSTS TOGETHER FOR SOCKETS IC36-IC44 AND IC31. WIRE LINES MOO-MOT FROM 24 PIN RIBBON SOCKET TO SOCKET IC36, MOUNTING THE EIGHT 100 or RESISTORS AS SHOWN BELOW.

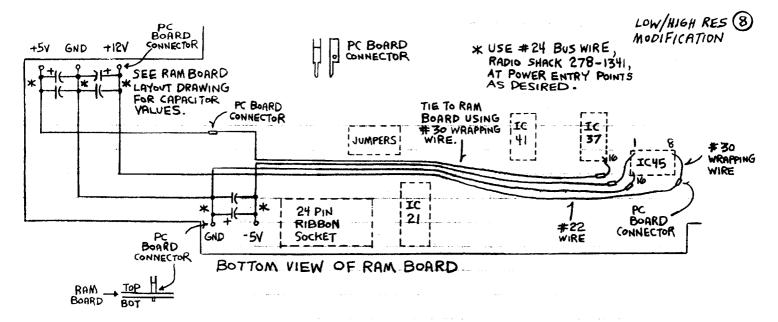

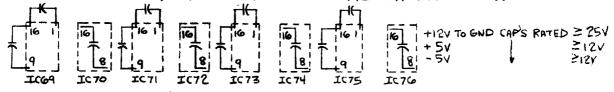

WIRE LINES MOO-MOT FROM SOCKET IC36 TO SOCKETS IC37-IC40. WIRE LINES DIQ-DIT FROM SOCKET IC36 TO RESPECTIVE SOCKETS IC45 - IC52. & GROUND POSTS 1 AND 19 OF SOCKET IC36 (WIRE TO POST 7 OF SOCKET IC31). WIRE THE EIGHT LINES DIO-DIT FROM SOCKETS IC37 - IC40 TO THE RESPECTIVE SOCKETS IC45-IC52. WIRE POSTS 14 TOGETHER, POSTS 2 TOGETHER AND POSTS 1,15 TOGETHER FOR SOCKETS IC37-IC40. WIRE POST 22 OF 24 PIN RIBBON SOCKET TO POST 1 OF SOCKET IC37. 8 TEMPORARILY GROUND POSTS 2 AND 14 OF SOCKETS IC37- IC40 BY WIRING POST 2 OF SOCKET IC40 TO POST 8 OF SOCKET IC44 AND BY WIRING POSTS 2 AND 14 OF SOCKET IC 40 TOGETHER. & WIRE THE +5V POST 16 OF SOCKET IC 37 TO THE + 5V POST 9 OF SOCKET IC 45.8 WIRE THE GND POST 8 OF SOCKET IC37 TO THE GND POST 16 OF SOCKET, IC45. 8 MOUNT JUMPERS SOCKET AND SOCKETS IC30 AND IC21.6 MOUNT THE SIX 33 1 RESISTORS NEXT TO SOCKET IC21. WIRE THE +5V, +12V, -5V AND GND WIRES AS SHOWN BELOW.

GROUND LINE AG OF THE FIRST BANK BY WIRING TO GETHER POSTS 13

AND 16 OF SOCKET IC45. WIRE THE +5V AND GND POSTS OF

SOCKETS IC30 AND IC21 TO THE RESPECTIVE +5V AND GND POSTS

OF SOCKET IC31. GROUND POSTS 1 AND 19 OF SOCKET IC21 BY

WIRING THEM TO POST 10 OF THE SAME SOCKET. WIRE SIX

LINES MAO-MAS FROM 24 PIN RIBBON SOCKET TO SOCKET IC21.

WIRE TOGETHER POSTS 8 AND 11 OF SOCKET IC21. SOLDER

FOUR RESISTORS TO THE BOTTOM OF THE SOCKET POSTS

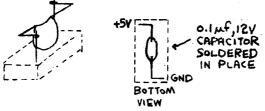

SOLDER, FROM THE +5V POST TO THE GND POST O. Juf 12V DISC CAPACITORS ON THE BOTTOM OF SOCKETS IC36-IC40 AND IC21.

IC45

WRAP A 4" LENGTH # 30 WIRE TO +12V POST 8 OF IC45 LEAVING

THE UNCONNECTED END UNSTRIPPED BUT NOT LAYING LOOSE.

THIS WIRE WILL EVENTUALLY BE CONNECTED TO +12V POST 8 OF

IC53. SOLDER O.Inf disc capacitors on the Bottom of

SOCKETS IC45-IC52 AS SHOWN BELOW.

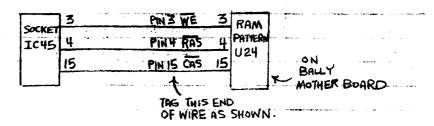

SOLDER 1200 & RESISTOR, AS SHOWN IN POWER SUPPLY SCHEMATIC, IN U28 RAM PATTERN. CUT 3 PIECES OF # 30 WRAPPING WIRE LONG ENOUGH TO MAKE THE CONNECTION SHOWN BELOW.

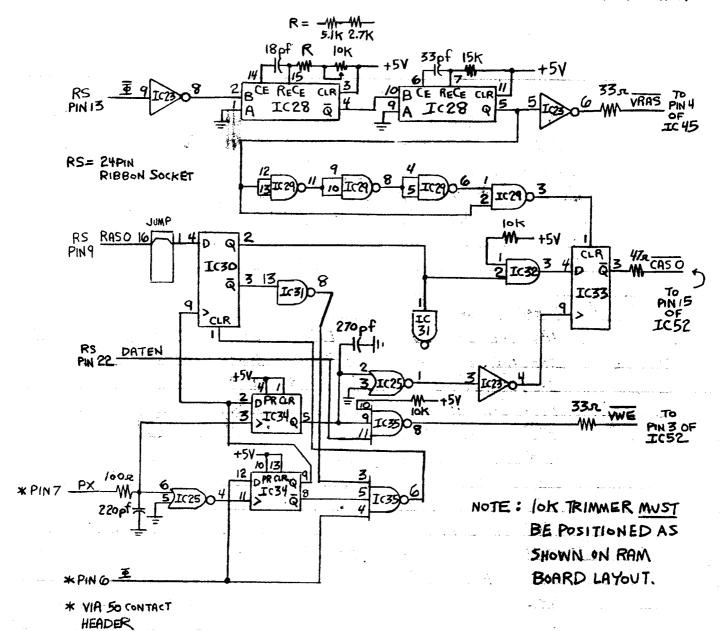

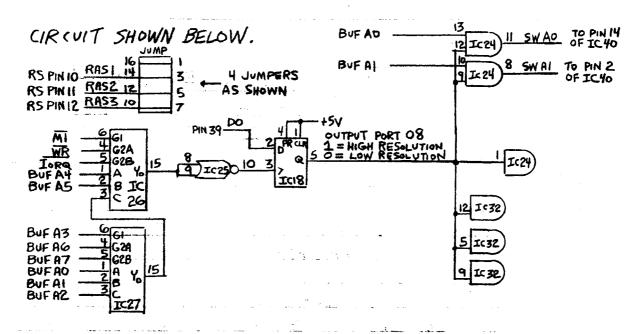

CONNECT ONE END OF EACH OF THE 3 WIRES TO SOCKET IC45 AS SHOWN TAG THE UNCONNECTED END OF EACH OF THE 3 WIRES. INSERT IC2/ IN ITS APPROPRIATE SOCKET. INSERT IC36-IC40 AND IC45 - IC52 IN THEIR APPROPRIATE SOCKETS, 4 MOUNT THE RAM BOARD AND BALLY MOTHER BOARD IN THEIR NORMAL POSITIONS (SEE PROCEDURE STEPS @ AND @). SOLDER THE 3 UN-CONNECTED WIRES TO RAM PATTERN U24. SEE NOTE 9. SEE NOTE 10. WHEN SYSTEM IS TURNED ON, THE MENU SHOULD BE ABLE TO BE DISPLAYED AFTER PRESSING THE RESET BUTTON. THE ON-BOARD GAMES WILL NOT FUNCTION AND WILL "CRASH". 2) REMOVE CHIP U22 (74LS74) AND RESISTOR R38 FROM MOTHER BOARD. CLEAN UP AREAS ON MOTHER BOARD TOUCHED BY SOLDERING IRON AND CHECK FOR SHORTS. DISCONNECT (BREAK CONDUCTOR PATH) LINE RASO FROM PIN 12 OF CHIP UZI (74LS 74) ON MOTHER BOARD. DISCONNECT LINES VIDOUT (PIN2) AND VIDIN (PIN3) FROM 50 PIN EXPAND BUS ON MOTHER BOARD. REMOVE THE 3 TAGGED WIRES, SHOWN ABOVE, FROM RAM BOARD. MOUNT SOCKETS IC 23, IC 22, IC28, IC29, IC9, IC35, IC5, IC34, IC25, IC32, IC33 AND IC77. MOUNT THE TWO 50 PIN HEADERS. WIRE THE +5V POSTS TOGETHER AND THE GND POSTS TOGETHER FOR THE 12 SOCKETS JUST MOUNT-ED. 8 WIRE THE +5V POST 14 OF SOCKET IC23 TO THE +5V PC CONNECTOR NEXT TO THE SOCKET ICLS. 8 WIRE THE GND POST 7 OF SOCKET IC23 TO THE GND PC CONNECTOR NEAR THE 24 PIN RIBBON SOCKET. & WIRE THE CIRCUIT SHOWN BELOW.

SOLDER, FROM THE +5V POST TO THE GND POST, O. INF 12V DISC CAPACITORS ON THE BOTTOM OF SOCKETS IC23, IC25 AND IC28-IC35. INSERT IC23, IC25 AND IC28-IC35 IN THEIR APPROPRIATE SOCKETS. SEE NOTE 9. SEE NOTE 10 AND ADVUST 10K TRIMMER TO GET THE COMPUTER TO RUN PROPERLY.

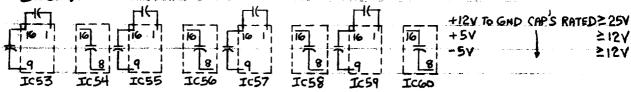

MOUNT THE SECOND BANK OF VIDEO RAM (SOCKETS IC53-IC60). 6,7

WIRE LINES VWE, VRAS, CASI, MAO-MAS, AG, -5V, +12V, +5V AND GND OF

SECOND BANK. WIRE LINES DIO-DIT FROM FIRST BANK TO SECOND

BANK. WIRE THE EIGHT LINES D20-D27 FROM SOCKETS IC37IC40 TO THE RESPECTIVE SOCKETS IC53-IC60. WIRE THE

-5V, VWE, VRAS, MAO-MAS, +12V, +5V AND GND POSTS OF SOCKET

IC45 TO THE RESPECTIVE POSTS OF SOCKET IC53. GROUND

LINE AGO OF THE SECOND BANK BY WIRING TOGETHER POSTS 13

AND 16 OF SOCKET IC53. WRAP THREE 4" LENGTH #30 WIRES

TO THE -5V POST 1, +5V POST 9 AND GND POST 16 OF SOCKET IC53

LEAVING THE UNCONNECTED ENDS UNSTRIPPED BUT NOT LAYING

LOOSE. THESE WIRES WILL EVENTUALLY BE CONNECTED TO THE

RESPECTIVE POSTS OF SOCKET IC61. SOLDER O. I LE DISC CAPACITORS ON THE BOTTOM OF SOCKETS IC53-IC60 AS SHOWN

BELOW.

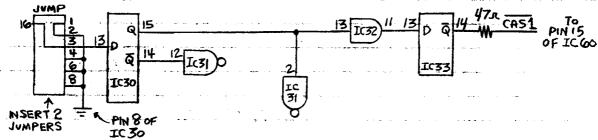

REMOVE THE JUMPER FROM THE JUMPERS SOCKET. MAKE THE CONNECTIONS SHOWN BELOW. 8

DISCONNECT THE "JEMPORARY GROUND" FROM POST 14 TO POST 2 ON

SOCKET IC40. INSERT IC53—IC60 IN THE SECOND BANK OF

SOCKETS. 4 SEE NOTE 9. SEE NOTE 10 AND READJUST 10K TRIMMER,

IF REQD, TO GET THE COMPUTER TO RUN PROPERLY (BANK 2 IS

OPERATING, BANK 1 IS INACTIVE).

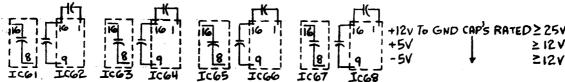

MOUNT THE THIRD BANK OF VIDEORAM (SOCKETS ICGI-ICGS). WIRE

LINES VWE, VRAS, CAS2, MAO-MAS, AG, -5V, +12V, +5V AND GND OF

THIRD BANK. WIRE LINES DIO-DIT FROM THE SECOND BANK TO THE

THIRD BANK. WIRE THE EIGHT LINES D30-D37 FROM SOCKETS IC37IC40 TO THE RESPECTIVE SOCKETS ICGI-ICGS. WIRE THE -5V, VWE,

VRAS, MAO-MAS, +12V, +5V AND GND POSTS OF SOCKET IC53 TO THE

RESPECTIVE POSTS OF SOCKET ICGI. GROUND LINE AG OF THE

THIRD BANK BY WIRING TOGETHER POSTS 13 AND 16 OF SOCKET

ICGI. WRAP TWO 4" LENGTH # 30 WIRES TO THE +12V POST 8

AND GND POST 16 OF SOCKET ICGI LEAVING THE UNCONNECTED

ENDS UNSTRIPPED BUT NOT LAYING LOOSE. THESE WIRES WILL

EVENTUALLY BE CONNECTED TO THE RESPECTIVE POSTS OF SOCKET ICG9. SOLDER O. Inf DISC CAPACITORS ON THE BOTTOM OF SOCKETS ICGI-ICG8 AS SHOWN BELOW.

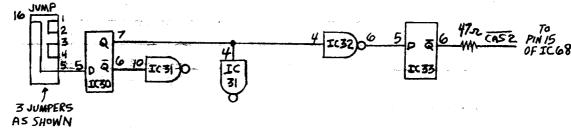

MAKE THE CONNECTIONS SHOWN BELOW. 8

DISCONNECT THE "TEMPORARY GROUND" FROM POST 2 ON SOCKET IC40, THEN GROUND POST 14 OF THE SAME SOCKET. INSERT ICGI-ICGS IN THE THIRD BANK OF SOCKETS. SEE NOTE 9. SEE NOTE 10 AND READYUST TOK TRIMMER, IF REG D, TO GET THE COMPUTER TO RUN PROPERLY (BANK 3 IS OPERATING, BANKS 1 AND 2 ARE INACTIVE).

MOUNT THE FOURTH BANK OF VIDEO RAM (SOCKETS ICG9-IC76). 6,7 WIRE LINES VWE, VRAS, CAS3, MAO-MAS, AG, -5V, +12V, +5V AND GND OF FOURTH BANK. WIRE LINES DIO-DIT FROM THE THIRD BANK TO THE FOURTH BANK. WIRE THE EIGHT LINES D40-D47 FROM SOCKETS IC37-IC40 TO THE RESPECTIVE SOCKETS ICG9-IC76. WIRE THE -5V, VWE, VRAS, MAO-MAS, +12V, +5V AND GND POSTS OF SOCKET ICG1 TO THE RESPECTIVE POSTS OF SOCKET ICG9. 8 GROUND LINE AG OF THE FOURTH BANK BY WIRING TOGETHER POSTS 13 AND 16 OF SOCKET ICG9. 8 SOLDER O. I LL DISC CAPACITORS ON THE BOTTOM OF SOCKETS ICG9-IC76 AS SHOWN BELOW.

MAKE THE CONNECTIONS SHOWN BELOW. 8

DISCONNECT THE TEMPORARY GROUND" FROM POST 14 ON SOCKET IC40.

INSERT IC69-IC76 IN THE FOURTH BANK OF SOCKETS. SEE NOTE 9.

SEE NOTE 10 AND READJUST 10K TRIMMER, IF REQD, TO GET THE COMPUTER TO RUN PROPERLY (BANK 4 IS OPERATING, BANKS 1,2 AND 3 ARE INASTIVE).

(5) MOUNT SOCKETS IC4, IC7, IC24, IC8, IC6, IC26, IC27, IC18, IC20, IC19, IC1-IC3 AND IC10-IC17. 6,7 WIRE LINES WE, RAS, CAS, A0-A7, +5V AND GND FOR SOCKETS ICIO-ICIT CONTINUING THE LINES FROM SOCKET IC14 TO SOCKET IC15 (WIRE IC11 TO IC13, IC13 TO IC16, IC/6 TO IC14, IC14 TO IC15, IC15 TO IC17, IC17 TO IC12, IC12 TO IC10). WIRE THE +5V POSTS AND THE GND POSTS OF SOCKETS IC4, ICT, IC24, IC8, IC6, IC26, IC27, IC18, IC20, IC19 AND IC1-IC3 TO THE RESPECTIVE +5V AND GND POSTS OF SOCKET IC9. " REMOVE TEMPORARILY THE THREE O. / DISC CAPACITORS FROM THE BOTTOM OF SOCKETS ICSE AND ICGO. 11 WIRE +5V AND GND POSTS OF SOCKET IC52 TO THE RESPECTIVE +5V AND GND POSTS OF SOCKET IC11. WIRE +5V AND GND POSTS OF SOCKET ICGO TO RESPECTIVE +5V AND GND POSTS OF SOCKET ICLD, SOLDER BACK THE THREE (APACITORS JUST REMOVED FROM SOCKETS IC52 AND ICGO. WIRE ALL OF THE CIRCUITRY SHOWN ON THE SOPIN EXPAND INTERFACE SCHEMATIC, USER RAM DECODER CHEMATIC AND USER RAM SCHEMATIC WITH THE EXCEPTION THAT PIN 1 OF IC24 SHOULD BE GROUNDED (TEMPORARILY). SOLDER O. INF DISC CAPACITORS TO THE BOTTOM OF SOCKETS ICI-IC20 AND IC24. TNSERT ICI-IC9, IC18-IC20, IC24 AND IC77 IN THEIR RESPECTIVE SOCKETS. INSERT IC10-ICIT IN THEIR SOCKETS. 4 MAKE SURE THE 50 CONTACTS OF THE 50 CONTACT EXPAND BUS ON MOTHER BOARD ARE CLEAN . SEE NOTE 9. SEE NOTE 10. SEE NOTE 12. ADJUST CAS DELAY IF REQ'D SO DEMO RUNS PROPERTY 13,14

26 REMOVE "TEMPORARY GROUND" FROM PIN 1 OF IC24. WIRE THE

SOLDER O. Juf DISC CAPACITORS TO THE BOTTOM OF SOCKETS ICEG AND ICET. INSERT ICEG AND ICET IN THEIR SOCKETS. SEE NOTE 9. SEE NOTE 10 AND READJUST THE 10K TRIMMER, IF REG D, TO GET THE COMPUTER TO RUN PROPERLY (BANK 1 IS OPERATING, BANKS 2-4 ARE INACTIVE).

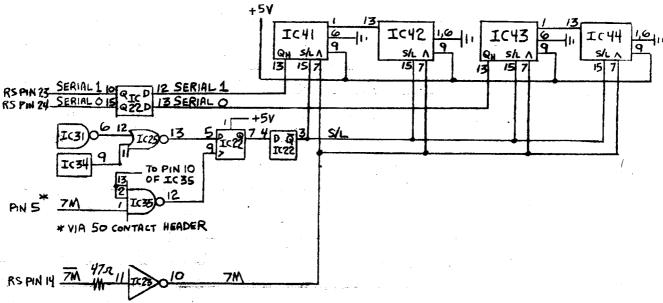

WIRE THE 32 LINES DID-DIT, D20-D27, D30-D37 AND D40-D47

FROM THE POSTS OF SOCKETS IC37-IC40 TO THE RESPECTIVE POSTS

OF SOCKETS IC41-IC44. WIRE THE CIRCUIT SHOWN BELOW.

SOLDER O. INF DISC CAPACITORS TO THE BOTTOM OF SOCKETS IC22 AND IC41-IC44. INSERT IC22 AND IC41-IC44

IN THEIR SOCKETS. SEE NOTE 9. SEE NOTES 10 AND 14. RUN THE GAME "CHECKMATE". WHILE THE GAME IS RUNNING, TURN, THE JOK TRIMMER CLOCKWISE YERY SLOWLY UNTIL THE GAME (COMPUTER) BECOMES INOPERATIVE. 18 NOW THE TRIMMER COUNTER CLOCKWISE SLIGHTLY AND PRESS THE COMPUTER RESET BUTTON. IF THE COMPUTER IS STILL INOPERATIVE, TURN THE TRIMMER COUNTERSLOCKWISE SLIGHTLY AGAIN AND PRESS THE COMPUTER RESET BUTTON. THIS IS THE STARTING POINT AT WHICH THE COMPUTER RUNS PROPERLY IN THE LOW RESOLUTION MODE. TURN THE TRIMMER COUNTER CLOCKWISE ABOUT 45° AND LOAD THE HIGH RESOLUTION DEMO INTO USER RAM AND RUN THE DEMO FOR 3 OR MORE HOURS. USE THE VERTICAL HOLD CONTROL ON THE TV TO SLOWLY ROLL THE PICTURE SO THE CRT WILL NOT BE "BURNED". CHECK FREQUENTLY THE SCREEN FOR GLICHES DURING THIS 3 HOUR TEST. NOTE THAT THE 4 BYTES IN SCREEN LOCATIONS YFEF, YFFO, YFFI AND YFF2 (IN UPPER QUARTER OF SCREEN ) ARE UTILIZED BY THE DEMO AND ARE NOT GLICHES. IF GLICHES DO OCCUR DURING THIS TEST, TURN THE TRIMMER IN ANOTHER POSITION. IF THE GLICHE PROBLEM CAN'T BE RESOLVED USING THE TRIMMER , THEIR MAY BE A RINGING PROBLEM AT PIN // OF IC 23.

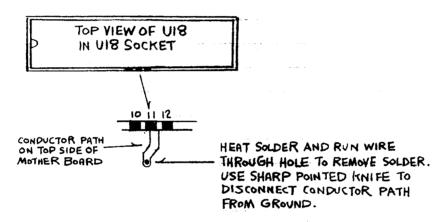

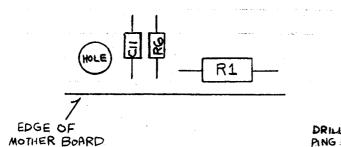

7M -W 1/230/0

TRY SOME DIFFERENT VALUES SUCH AS 68,82 OR 100 OHMS IN LIEU OF 47 OHMS.

- WIRE THE UNUSED INPUTS OF THE SPARE GATES INDICATED ON THE SPARES SCHEMATIC.

- THE FOLLOWING MODIFICATIONS TO THE MOTHER BOARD ARE OPTIONAL.

REMOVE CAPACITORS (52-(55. 15 REMOVE CAPACITORS (56-(61. 15

REMOVE RESISTOR R37. REMOVE RESISTORS R40-R42. REMOVE

CAPACITORS (67-(77, (80-(84, (91 AND CIOCO. 16 REMOVE CAPACITORS

(62-(64. USE# 30 WRAPPING WIRE TO SOLDER THE FOLLOWING UNUSED

INPUTS TO +5V. +5V

REMOVE CHIP UZI (74L574).

30 AT THIS POINT YOUR COMPUTER SHOULD RUN PROPERLY IN THE LOW

OR HIGH RESOLUTION MODE. AN OUTPUT OIL TO PORT 8 TELLS

THE CUSTOM CHIPS TO MAP THE SCREEN RAM IN HIGH RESOLUTION

AND RESPECTIVELY AN OUTPUT OOH TO PORT 8 TO MAP THE

SCREEN RAM IN LOW RESOLUTION. REFERENCE DAVE

NUTTING ASSOCIATES MANUAL P.81-91 FOR GENERAL

SYSTEM DESCRIPTION.

## NOTES

- 1 TURN ON THE COMPUTER TO SEE IF ITS OPERATING PROPERLY, IR,

PUSH THE RESET BUTTON, ENTER 2, O AND O TO RUN THE GAME

"CHECKMATE" FOR A WHILE.

- 2 SCREEN GLICHES MIGHT APPEAR OCCASIONALLY. THE COMPUTER MIGHT EVENTUALLY WONDER OFF INTO "NEVER-NEVER LAND".

- 3 THE MOTHER BOARD CAN OPERATE WITHOUT THE KEYBOARD HOUSING OR METAL SHIELDING. HOWEVER, MAKE SURE THERE IS A HEAT SINK ON TOP OF CUSTOM DATA CHIP VIS OR BLOW AIR ACROSS THE MOTHER BOARD VIA A PORTABLE FAN.

- 4 BEWARE OF DESTROYING THE CHIP (S) BY STATIC ELECTRICITY. HANDLE WITH CAUTION.

- 5 DESIGNER MOUNTED BALLY ARCADE ON A VIPER CABINET.

- 6 USE 2-56 × 14" SCREWS AND 2-56 × 3/6" × 16" HEX NUTS BOTTOM OF SOCKET SHOULD MOUNT FLUSH WITH RAM BOARD, OTHERWISE SOCKET MAY CRACK WHEN SCREWS ARE TIGHTENED.

- 7 FOUR LEVEL (≥0.625" POST LENGTH) WIRE WRAP SOCKETS SHOULD BE USED.

- 8 USE OHM-METER TO TEST WIRING PERFORMING THE TEST ON THE TOP OF SOCKETS (WHERE IC IS INSERTED).

- 9 MAKE ALL NECESSARY CONNECTIONS SO RAM BOARD AND MOTHER BOARD CAN BE TURNED ON: +5V,+12V,-5V AND GND CONNECTED TO RAM BOARD (-5V COMES

FROM BALLY MOTHER BOARD- SEE POWER SUPPLY SCHEMATIC).

24 PIN DIP JUMPER CONNECTED FROM RAM BOARD TO MOTHER

BOARD.

50 PIN RIBBON (ABLE CONNECTED FROM RAM BOARD TO MOTHER BOARD.

BALLY POWER TRANSFORMER CONNECTED TO MOTHER BOARD.

RF MODULATOR CONNECTED TO MOTHER BOARD.

HEAT SINK CONNECTED TO CUSTOM DATA CHIP U/8 ON

MOTHER BOARD. SEE NOTE 3.

TO TURN ON RAM BOARD AND BALLY MOTHER BOARD SIMULTANEOUSLY.

The profit of the second of th

DESOLDER THE IC SOCKET POSTS USING DESOLDER TOOL

RADIO SHACK CAT # 64-2098 OR EQUAL. DO NOT FORCE WRAPPING

TOOL OVER SOLDERED POST, BUT PRESS LIGHTLY DOWNWARD WITH

A TURNING MOTION.

- 12 LOAD LOW RESOLUTION DEMO INTO USER RAM AND RUN

THE DEMO. IF DEMO DOESN'T RUN CORRECTLY, THE PROBLEM IS

MOST PROBABLY AN IMPROPER CAS DELAY.

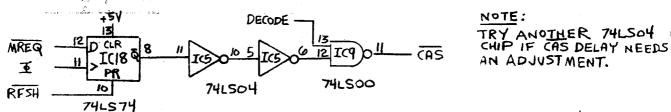

- 13 TIMING OF CAS IS CRITICAL. BOARD LAYOUT, LOADING EFFECTS

OR TOLERANCES ON (HIP PROPAGATION DELAY CAN EFFECT THE

TIMING OF CAS. THE ADJUSTMENT TO THE CAS DELAY IS MADE

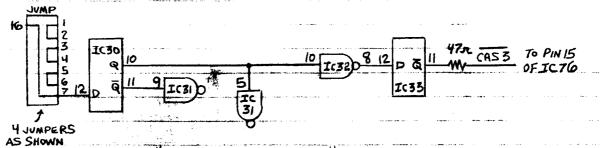

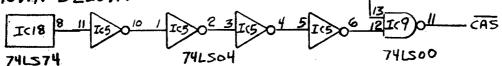

ON THE CIRCUIT SHOWN BELOW.

THE DELAY CAN BE INCREASED OR DECREASED BY ADDING DELETING GATES OR BY UTILIZING 74S IN LIEU OF 74LS TTL. FOR EXAMPLE, THE DELAY CAN BE INCREASED BY ADDING TWO GATES AS SHOWN BELOW.

DECODE —

ADDING TWO GATES AS SHOWN ABOVE WOULD INCREASE THE DELAY OF CAS AS LONG AS 20 ns (1981 NATIONAL SEMICONDUCTOR. DATABOOK). IMPROPER TIMING OF CAS (AN CREATE GLICHES ON THE SCREEN OR "CRASHES" WHEN A PROGRAM IN USER RAM IS EXECUTED. IF IMPROPER TIMING OF CAS IS SUSPECTED, THEN AN EXPERIMENTAL ADJUSTMENT IS NECESSARY.

- 14 A POOR CONNECTION FROM THE 50 CONTACT EXPAND BUS ON MOTHER BOARD TO 50 CONTACT HEADER ON RAM BOARD WILL CAUSE THE SYSTEM TO OPERATE IMPROPERLY.

- 15 TAG COMPONENT FOR USE AS A SPARE PART. MANUFACTURER MAY HAVE DELETED COMPONENT FROM MOTHER BOARD.

- 16 TAG COMPONENT (S) FOR USE AS SPARE PART (S).

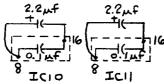

- 17 SOLDER A 2.2 MF TANTALUM (APACITOR (RADIO SHACK (AT. #272-1435 OR EQUAL) TO THE BOTTOM OF SOCKETS IC/O AND IC/ OBSERVING POLARITY OF CAPACITOR

- 18 DUE TO TOLERANCES IN 74LS123 (HIPS (ICI8), THE lok TRIMMER COULD BE TURNED FULLY CLOCKWISE AND STILL THE SYSTEM WOULD BE OPERATIVE.

- 19 REFERENCE BALLY SERVICE MANUAL PA-1 DISASSEMBLY PROCEDURE.

- 20 RUN LOW AND HIGH RESOLUTION DEMOS TO TEST THE SYSTEM. IF

THE VIDEOCADES RUN PROPERLY, BUT THE LOW RESOLUTION DEMO

DOES NOT, REFER TO NOTES 14, 12 AND 13 (USER RAM IS AT FAULT).

IF VIDEOCADES AND LOW RESOLUTION DEMO RUN PROPERLY, BUT

HIGH RESOLUTION DEMO DOES NOT, REFER TO PROCEDURE STEP .

NOTE THAT BANK 1 (1645-1652) IS THE LOW RESOLUTION RAM BANK.