# R&L

# 64K RAM Board

This documentation originally had even numbers on the front and odd numbers on the back of each page. This new cover has been added so that the new pages conform to the normal front and back numbering conventions.

### GENERAL HARDWARE FEATURES

#### "BOAST PAGE"

This is the page where the manufacturer tells you how good the unit is, how much better it is than anyone elses, and why it's just the greatest thing in the world. (And other B.S.) So any use anyone makes of this information is only what they make of it. (We like to think it's possible B.S.) But since conversation, planning, and creation exist,...some bits should be supplied here.

Since we've tried to design this board keeping in mind the programmer, experimenter and teacher, we're going to make our...

- \*\*\* COMPLETE SYSTEM DOCUMENTATION

- reflect this. We've provided more than the information that is needed to simply use (play with) this device. Rather than make promises about future developments we'll just say that if we were developing software the same would hold true in this area. From the looks of it though...

- \*\*\* 24 PIN MEMORY DEVICE INTERCHANGABILITY

means you can replace RAH with ROH at any time which could provide a users utility

library to be easily accessed from some form of BASIC.(? Hmmm)

Ram or Rom x 2K... The choice is yours. Notice the...

- \*\*\* LOGICALLY ORIENTED BOARD DESIGN

- \*\*\* BALLY/ASTRO BUSS DUPLICATED ON A SECOND EXPAND JACK to allow for immediate further expansion.

- \*\*\* 32 SWITCH MEMORY ENABLE/DISABLE (One for each socket)

means there is 1 switch for each 2K location, and is also providing external disable for every switch that is <u>ON</u>. (Board becomes "phantom" at user defined locations)

- \*\*\* CAN BE POWER FAIL PROTECTED

with one resistor 2 diodes and your choice of rechargable battery. (Plans included)

- \*\*\* 4 or 16K MAGIC OPTIONS

This means Hi-Res. MAGIC memory will be usable with Hi-Res. systems, and that there are lower 4K, or lower 16K write protect options.

- \*\*\* 64K WRITE PROTECT OPTION

Any further external memory which is added opens you up to the option of using the 64K memory board as a write protected block. (While the added memory can be used for read/write/scratchpad) in fact...

- \*\*\* EXISTING ADD-ONS CAN STILL BE USED

meaning they will not go completly to waste. For example, the Blue Ram can be

directly plugged onto the second expand connector for use of the 8154's 1.0. ports.

(Provided the memory is disabled)

- \*\*\* SIMPLE VERSATILE FIRST SATURATION OF Z-80

No unnecessary added gimicks or gremlins, giving you a reliable, Fully Static,

1'st solution to the software problem. (Ever had this much room?!)

- \*\*\* EXPERIMENTERS AND HOBBYISTS HAVE NOT BEEN FORGOTTEN

Here is some off the wall "creative conversation" for you hardware wizards---

"Notice the holes..." "Makes you want to think DMA, or vectored address memory bank selecting..." "Makes me want to think user defined MAGIC memory attachment kit..." If you think other things - feel free to do it...that's what they're there for. Though further expansion for a dedicated peripheral will be done through the second expand jack. (Don't worry...there will be a third one.)

"If a 12K BASIC were developed scratchpad would be..." "A utility might steal some space over Gunfight Checkmate & Calculator..." "...and anything else you can imagine could probably be easily done." ... Someone said while staring at the 50 holes. So you could say this hardware is....

#### GENERAL HARDWARE UNFEATURES

#### "SORRY PAGE"

This is the page most manufacturers make obscure. (For one reason or another) This is where you can find out any possible drawbacks which we have been able to think of, and just what can and can not be expected from this unit.

MEMORY IS FAIRLY EXPENSIVE \*\*\*

...oh well

BOARD LOGIC DOES NOT "PHANTOM" (on power off) \*\*\*

You will not be able to immediatly plug on another control or memory device and power-down ("Float or tri-state") the whole 64K RAM board. This can only be done with the internal switchpaks when the unit is 0N. (You can't deselect data buss if the board is powered down. Unit must be 0N if connected to the 50 pin connector.) External memory can be plugged on provided the proper switches are selected OFF in its ranges on the RAM board.

NO HI-RES VIDEO \*\*\*

There is no way to get Hi-Res from this board without hacking it and providing externally synchronized video. (For that matter you can't get Hi-Res out of the Arcade without major hardware hacking on the mother board, and creation of proper software to run in it.)

DOES NOT PROVIDE BANK SELECTING OR MORE "MAGIC" MEMORY \*\*\*

Pon't expect to immediatly overlap memory ranges from the second expand jack. I trust you understand this. (This doesn't mean it can't be done.)

NO ADDRESS SWAPPING LOGIC HAS BEEN PROVIDED \*\*\*

Unlike the other available memory devices, this board can not switch memory located @ 24576 to 8192. (The cartridge slot) Nor is any other "Relocation of memory" logic provided. Each socket has its own seperate address range, and select switch for that range and socket only.

FURTHER HARDWARE COMPATABILITY NOT INSURED \*\*\*

Just because now existing memory devices can be used, doesn't mean you'll be able to add this unit between the Home Video and the coming (?) add-under. (Chances are... whateven they do... it can be kludged (SORRY) to the add-under as "add-between" memory.)

#### HARDWARE OPTIONS

- 1. Full 64K write protected. (See pq.4) 主

- 2. Lower 4Kior lower 16K+write protect. (See pg. 4)

- 3. Battery backup.(See pg.3) 🛣

- 4. 24 pin memory device interchangability. (See pg.11)

- Seperate enable/disable control for each socket.φ(Assures microcyclor/ROM disable when sw. is ON.)

- 6. Second expand jack allows continued expansion easily. ♥ (1.0./control/memory) Also prototyping holes/area is provided for all 50 buss conections.

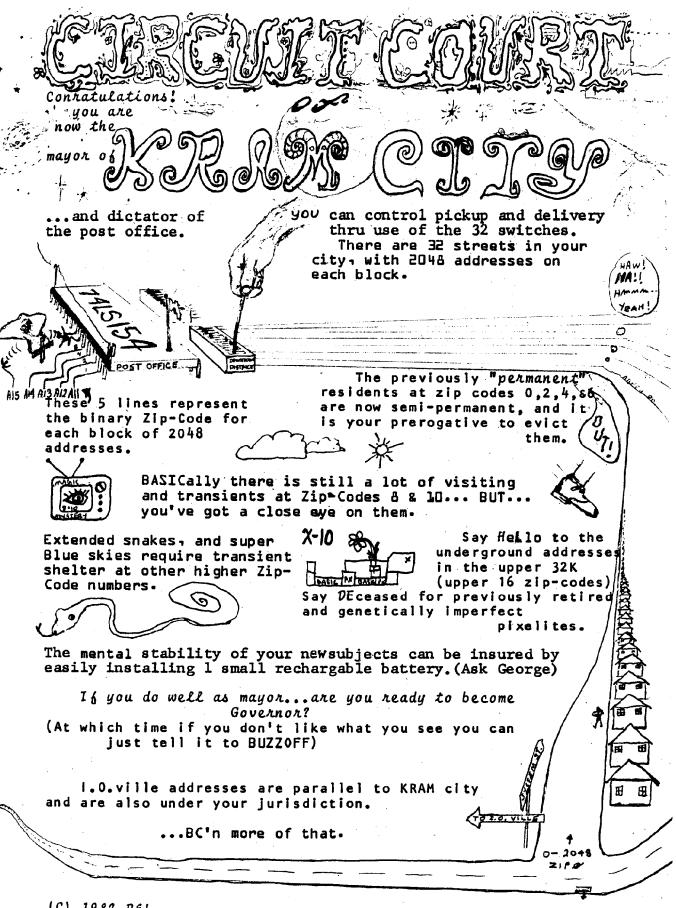

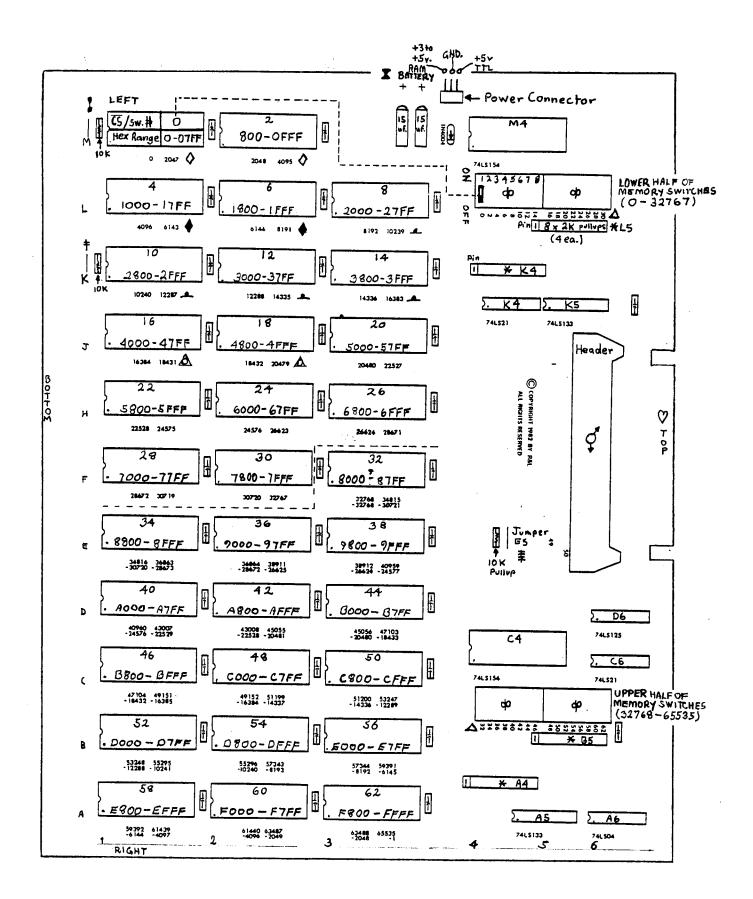

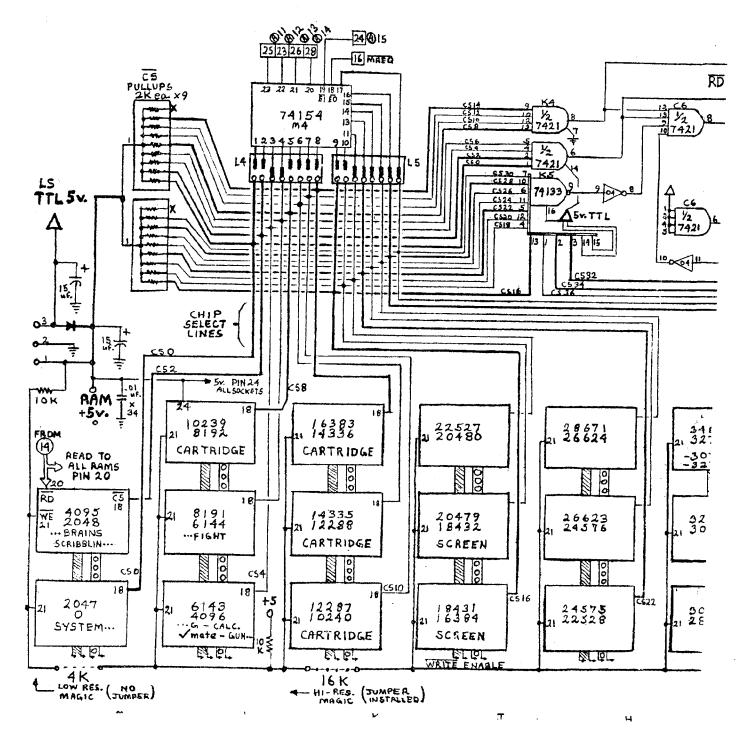

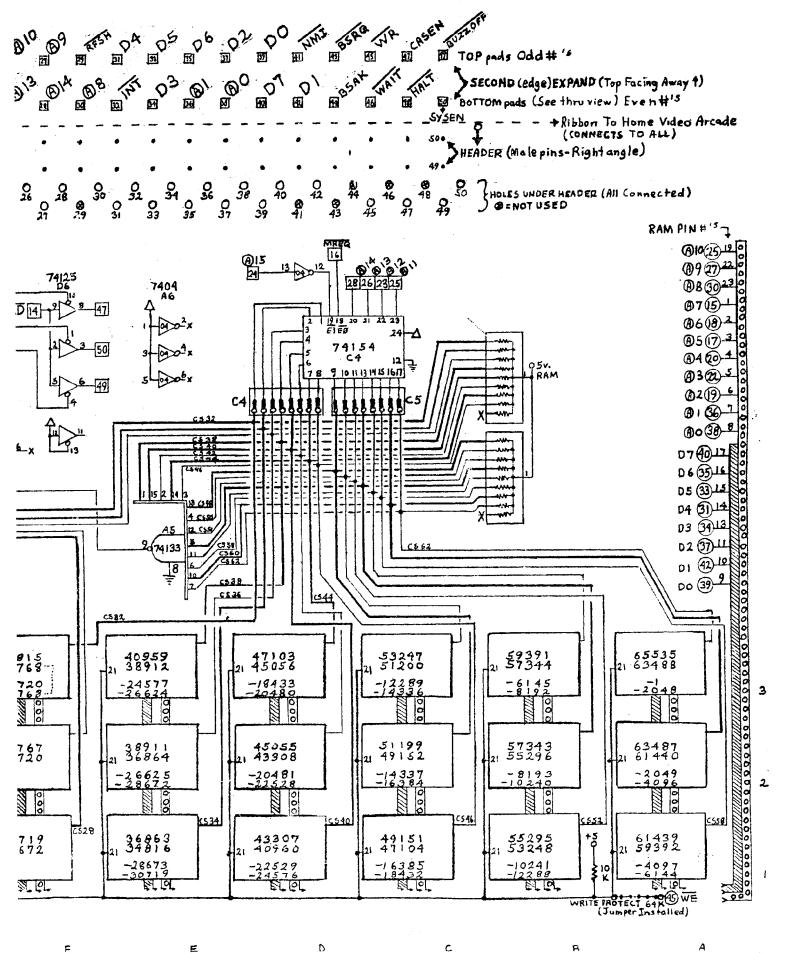

#### ADDRESSING RANGES

The numbers silk-screened to the right of the switchpaks represent the approximate starting address of its associated socket. For convenience this is also the chip select numbering system. Starting from 0, the switches and sockets are arranged from bottom to top - left to right. The exact address range of each chip is silk-screened to the right of each socket.

The first two sockets, (First 4K of memory) cover the range  $\Diamond$  of the operating system ROM in the Home Video. This is probably going to be used for now, so these first two switches (0 & 2) should be in the OFF position. (For more details see the section on Magic Memory.)

The second 4K block, (Sw.'s 4 & 6) cover the range of ♠ calculator, checkmate, and gunfight. These may be scratched if desired by installing memory in these two sockets and turning the switches ON. (so any device here can respond instead)

The next 4 sw.'s , (8-10-12 & 14) cover the 8K cartridge range (8192-16383) and should be in the 0FF position if you expect to use the cartridge slot.

Switches 16 & 18 cover the range of screen memory and  $\Delta$  should be left in the OFF position, with no memory devices installed here for now.

The rest of the available locations may be filled with memory as desired. This amounts to 45056 bytes of memory represented by sw.'s 20 thru 62. 49152 bytes are available if the 4K of onboard games are scratched, and 57344 bytes are available if no cartridges are being used.

Memory may be left plugged in the sockets for the cartridge range so long as the switches are in the OFF position when using a cartridge. At least one sw. in this range must be OFF when using a cartridge. (sw.8 for 2K cart.) Sw.'s 8 & 10 must be OFF for a 4K cart. and 8-10-12 & 14 for an 8K cart.

- REMEMBER---1. If you switch the range OFF the RAM board will do nothing. (Externals may respond)

- 2. If a switch is ON the RAM board will attempt to execute the read or write being done in this range to the associated socket, and will provide the appropriate disable signal for that range.

#### POWER SUPPLIES

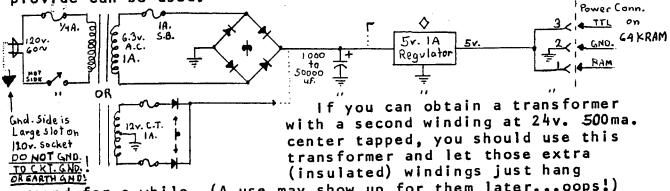

Any of the following supplies are recommended to power the 64KRAM board. Alternativly any 5v. 1A. supply which you provide can be used.

around for a while. (A use may show up for them later...oops!)

The secondary windings specified can be taken to +10, 20%.

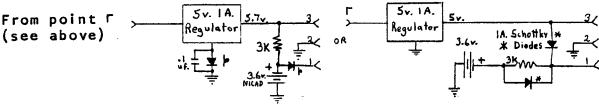

The following circuits can be used to create a batterying RAM supply. (Provides power fail protection to preserve 64 KRAM memory contents during Commonwealth Edison freakouts)

Pre-canned 5v. supplies will require the schottky diode implementation. They must have a small maximum forward voltage drop. (See recommended parts list below.) Each NICAD cell produces about 1.2v.. 2.4v. worth will work, but memory retention becomes less stable below 2v. so you should use 3.6v. (3-cell) or 4.8v. (4-cell). A 1A. Germanium diode will give even better results in place of the Schottkys, but a 1A. er may be hard to find since germaniums' were the next invention after cats whiskers. (They have only .2v. of forward voltage drop.)

♦5v. 1A. Regulator- 7805, LM340T5

\*Schottky diode 1A - G.I. SB340,MC7805C,or 1N5817

Battery - 3 "C" cell size NICADs. 1A.H. rating. NOTE: Use the germanium diodes when using 4 cells.

Transformer - 6 to 10v. @1A. (Try Radio Shack)

- 12 to 20v. C.T. @1A.

- Combination windings for + & - 12v. supply

\*Germanium diode 1A. LOST & FOUND. still looking.

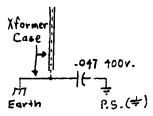

The following information may be completely ignored unless you insist on earth grounding your system. The diagram below shows how to properly terminate the third wire ground to the transformers in your system. If any single earth ground is added it is imperative that all other transformer supplies be

3 wire plug court stack as a stac

terminated in a similar manner. WARNING! DANGER! FLASHING RED LIGHTS! Don't forget that the home video does NOT provide any third wire ground.

Other things which you have just read and may also be ignored are the plug polarity, (to 120v.) and the fuses. These are merely included to illustrate the proper way of connecting A.C. source voltage to any appliance. P.S. If you look inside some of the appliances around your home you will find about 50% of them to be hazards. But then...if shock, lightning, and fire hazards don't scare you...you may find external dynamic memory that disagrees. (...if you have funny electricity in your area.)

It is a good idea to insulate the transformer case from the power supply and circuit ground, connecting the third wire, or Earth GND. to the transformer case only. (With the added neutralization in the circuit shown above.) However now if you are downline on a run of conduit that has high current inductive loads which are switching on and off... Transients on the Earth ground may find their way into your circuit ground through transformer capacitance. The following circuit is claimed to alleviate this problem without connecting earth ground to power supply ground directly.

The power supply ground to earth gnd. connection should be made at a point close to actual power supply ground, before the wires running to your RAM board power connector. (This will prevent a ground loop through the logic/ckt. ground.)

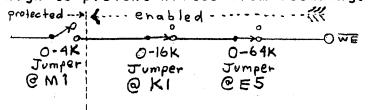

#### WRITE PROTECT INSTALLATION

There are three areas of memory which may be write protected with the installation of a switch where the jumpers go. When the switch is opened (OFF) the write line is disconnected from all memory below that point, protecting its contents. The 10K resistor holds the write pins on the memory devices high to prevent writes from occuring.

The 10K resistors are already on the board, and you may simply install a single throw single pole switch in at each area of memory

you wish to make write protectable. (Remove the jumper in that range, and run some thin wire to the switch.)

## ROUTINES FOR ACCESSING UPPER ADDRESS RANGES WITH BALLY OF ASTRO BASIC

The following routines are provided to allow the old basics to access the upper (negative) addresses, to or from pixel shared or single byte memory storage. The old Basics interp negative addresses as pixel shared (text area) memory.

Input the following decimal numbers with the following command statement. (The code is relocatable, and may be used from within a BASIC program. A good place to put it is over "FIGHT" 6144-8191. Install a RAM here and flip CS sw. 6 to the ON position.);

```

FOR A=6144TO 6210; PRINT A,; INPUT""%(A); A=A+(%(A)>255); NEXT A

Enter these

numbers

; Move to normal memory from pixel shared.

207,44,62

0-RST 1

3-RST 2

215

4-PUSH HL

229

5-RST 1

207,44,57

8-RST 2

215

9-LD A.L

125

10-LD B.H

68

11-POP HL

225

12-LD(HL),A 119

13-INC HL

35

14-LD(HL),B 112

15-RET

201

; Move to pixel shared from normal memory.

16-RST 1

207.44.46

19-GET Adrs 205, (10713) or (8947)

B.B.

A.B.

22-PUSH HL

229

23-RST 1

207,44,39

26-RST 2

215

27- KSP) .HL

227

28-POP BC

193

29-LD A, (BC) 10

205.(12263) or (12258)

30-STRPS

B.B.

A.B.

33-INC HL

35

34-INC BC

35-LD A,(BC) 10

36-STRPS

205, (12263), or (12258)

39-RET

:Absolute block move-(normal to normal)

40-RST 1

207,44,22

43-RST 2

215

44-PUSH HL

229

45-RST 1

207,44,17

48-RST 2

215

49-PUSH HL

229

50-RST 1

207,44,12

53-RST 2

215

```

continued ...

54-PUSH DE 213 55-POP IY 253,225 57-POP DE 209 58-POP BC 193 59-LDIR 237,176 61-PUSH IY 253,229 63-POP DE 209 64-RET 201

;Jump to WHAT? if no char match. 65-JMP nn 195,(10611) or (10694) B.B.

To use these routines the following structure is used. "S" is the starting address of where you loaded these routines. Move from pxshrd. to normem.

CALL Ø+S,A,D

A=Absolute address to write to D=Data to be written from pxshrd. (May be  $2(-\frac{1}{100})-0-\frac{1}{100}$ . The routine will copy two bytes at a time, so loops and counters should be stepped by 2.

EXAMPLE; Enter line 10...... Then D=-24576 (To point to first pixel shared byte of BASIC program in text area.) Then enter; FOR A=(absolute address where you have some memory to copy to:M")TO M+(1800-SZ)STEP 2; CALLO+S(61447),A,%(D); D=D+2; Your BASIC program is now stored in single byte locations starting at the absolute address you entered. Don't forget \* or @ values, and your end of program storage number (20050 for B.B. & 20000 for A.B.) if you intend to use this routine to store multiple BASIC programs in your memory.

You may check to see that the routine worked properly now by TVing out the characters from the memory you loaded it to as follows. FOR B=(where you loaded it to) TO A:TV=%(B):NEXT B The two "?" are the line number, and will be restored if the following routine is used to load the program back to the text area. (The line number is stored as binary and is not a TVable character.)

Move from normem to pxshrd.

CALL 16+S.D.A A=Absolute address to read from(normem) D=The BASIC pxshrd. address to store the data at. (Also reads a word - 2bytes) EXAMPLE; This will load the normem stored BASIC program back to pxshrd.(text area). D=-24576; FOR A=M TO M+(1800-SZ) STEP 2; CALL 16+S, %(D), A; D=D+2; NEXT A LIST the program now to check the operation of this routine. If your routines were entered at location 6144, and the BASIC program is in normem starting at location 24576, the statement would read as follows; ....CALL6144+16,%(D) - from -24576 - , A - from 24576;...etc.

Last but not least is the absolute block load routine which is used for various duties such as just moving things around in normem. For example, you could use it to store the complete BASIC program and picture, (including the end of text pointer) to a 3720 byte block of normem somewhere. It can then be loaded directly back to screen memory with this same routine when its use is required.

## Absolute block move. (normem to normem) CALL 40+S,B,D,S B=The byte count

D= The destination address

S= The source address

To test this let's say you have a BASIC program loaded, and you want to store it w/picture & pointers in 3720 bytes starting from a normem location of 24576. The following command will do the trick; CALL 40+6144,3720,24576,16384 (Screen memory) The following command will load it back...ready to RUN again. CALL 40+6144,3720,16384,24576

#### LANGUAGE MEMORY LOCATIONS

| Lang.                                                 | Lang.@                                    | Req.Read /                                    | Write @                                |        |

|-------------------------------------------------------|-------------------------------------------|-----------------------------------------------|----------------------------------------|--------|

| ASTRO BASIC<br>BALLY BASIC<br>Viper Ext.<br>Blue Ext. | 8192<br>8192<br>24576-32767<br>8192-16383 | ** Screen<br>** Screen<br>-32768 t<br>24576 t | ** · · · · · · · · · · · · · · · · · · | H      |

|                                                       | USEFUL LANGUAGE                           | LOCATION                                      | NUMBERS                                |        |

| Lang.                                                 | ASTRO                                     | BALLY                                         | B/R                                    | VIPER  |

| Get address                                           | 8947                                      | 10713                                         | 10323                                  | 31286  |

| STOP                                                  | 9540                                      | 9372                                          | 8640                                   | 25024  |

| Evaluate xpr.                                         | 8202                                      | 8202                                          | 15566                                  | 31679  |

| Solo (; sp.)                                          | 8905                                      | 10588                                         | 14896                                  | 31280  |

| Skip space                                            | 8208                                      | 8208                                          | 14902                                  | 31286  |

| Get pxshrd.                                           | 8205                                      | 12239                                         |                                        |        |

| Store pxshrd.                                         | 12258                                     | 12263                                         |                                        |        |

| Variables @                                           | 20002                                     | 20078                                         | 27818                                  | -29526 |

| Check Char.                                           | 8199                                      | 8199                                          | 14909                                  | 31293  |

| Exit instr.                                           | 8214                                      | 8214                                          | 9312                                   | 25696  |

#### INSTALLATION

- 1. Connect suitable 5v. supply to the RAM board. and plug on the double female connector to the header as shown below. Be sure to watch the polarity of the power connector if you have installed Directly to Female (large) to Arcade a battery backup system.

- 2. If the 50 pin connector knockout has on back of Arcade Ribbon Cable not been removed from the rear of the Directly to Arcade, bend it back and forth gently header on back Female (small end) until it breaks off.

- 3. Push down the cardboard insulator under the Home Video expand jack to make room for the large female connector.

- 4. Set the Arcade down on top of your 64KRAM case and flip up the 50 pin female connector so it aligns with the Arcades 50 pin edge connector. Then slide it on evenly and firmly.

- 5. Power may now be applied to both units.

NOTE: If you have memory installed in the ranges specified for an extended language, be sure the CS switches are ON in those ranges. (See pg. 7 on addressing ranges for languages.)

#### PRECAUTIONS AND STANDARD OPERATING PROCEDURES

- 1. Do not expose the unit to extreme heat, humidity, or other harsh environments such as chemical vapors, fumes, and smoke.

- Do not touch metal parts to any of the exposed foils when the top of the case is open. (Make sure there is nothing around that can accidentally fall into the unit.)

- 3. Do not overlap memory ranges, when connecting externals. The switches must be properly selected. (See section on addressing ranges and also Magic Memory.)

- 4. Standing alone, having any of the switches in the wrong position for the purpose which you intend to use it, will not cause damage. (But don't expect it to work.)

- 5. Shock, vibration, Coca Cola, and bulldozers are not allowed.

- 6. Try to use some type of non-conductive article to flip the CS switches. (Under normal operating circumstances these switches should not be futsed with.)

- 7. Watch out for stray metal articles which may decide to roll into the rear of the KRAM over the second expand jack.

- 8. Static, \*Hot chassis, and lightning are also not allowed. (\* This means if you can touch your T.V. and a grounded water pipe and not see stars...you may connect the unit.)

- 9. When connecting other peripherals to the second expand, be sure the connector goes on straight. (It is advisable to have the power off if you have been known to be klutzy.)

- 10. If you smoke, you should take large doses of Vitamin C and Niacin every day.

#### CIRCUIT DESCRIPTION

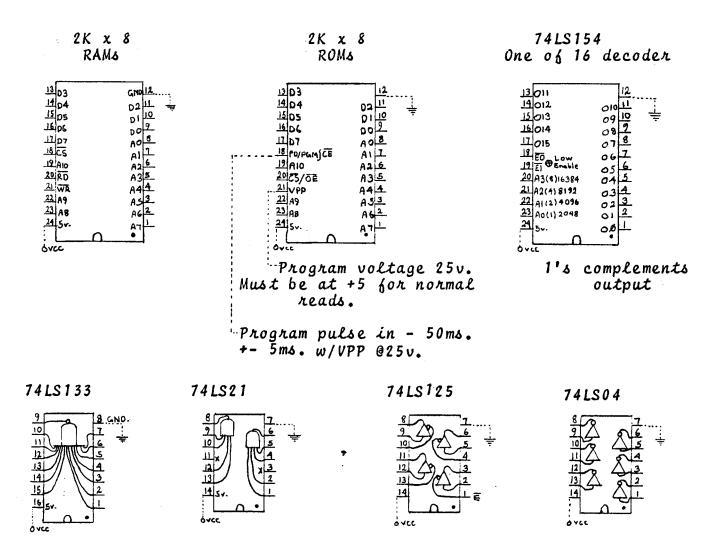

The TTL components for chip select and external disable (While board responds @ that address) are all 74LS (Low power Schottky) The memory devices (ROM/RAM) are all CMOS 2K x 8 bit. See pg. 11 for component listing.

- 74LS 154 This chip is responsible for decoding the incoming M4 & C4 address to the proper memory device socket. Also is the origin of output deselect signal.

- 74LS 21 Provides decoded output for disabling system ROM in one half, and an output for disabling cassette ROM in the other half. It derives these outputs from switches that have been selected (ON) in these address ranges. (From 154 in 2K blocks)

- 74LS 133 Provides external deselect signal (BUZZOFF) for any K5 & A5 other memory which may be around. (ex. Disables screen memory (Microcyclor buss) to allow RAM board to respond @ these addresses.) Any switch which is ON will provide this signal on access to that range. Allows external memory to reside at addresses which have not been selected on the RAM board by not outputing a disable signal. (If sw. is OFF)

- 74LS 21 1/2 used for decoding complete external system c6 enable/disable signals. This is to insure SYSEN CASEN and BUZZOFF "float" by providing this signal to the tri-state enable, input of the following device (125).

- 74LS 125 Provides tri-state outputs for the control signals

D6 CASEN, SYSEN, & BUZZOFF. It allows the read (RD)

signal to appear as the output to these control lines

during memory board accesses in the ranges selected.

- 74LS 04 Provides signal inversions where necessary, A6

## CIRCUIT OPERATION (See schematic)

The left side 154 (M4) is providing the socket (memory) decoding for the lower half of memory. (0-32767) When A 15 and MREQ are low at the same time this chip is enabled (pins 18 & 19) and address decoding appears on the one of 16 outputs. If A 15 is high the other 154 (C4) decodes the upper half of the addresses. (32768-65535)

Starting from A 11 (2048) the addresses are decoded in steps of 2K blocks. A 11 thru A 14 are connected to the 154's inputs providing the one of 16 Chip Select thru any switch which may be 0N.

Switches that are not ON are pulled up by the inline resistor network on the CS side. This is to insure memory device deselection ("Float" to tri-state) if that 2K address range is not ON. (Data buss disappears if CS is high)

The one of 16 outputs are also decoded by the 133s and the 21s to provide proper external deselection in ranges that are switched ON. BUZZOFF is active (low) during any access to the RAM board. This signal disconnects the microcyclor data buss from the Z-80. (Custom chip data buss is disabled.) Writes to system or cassette ROM are disabled by the Home Video hardware. (Controlled by state of RD.)

So any access to the board will enable one of the sections (Tri-state buffers) of the 125. Whether or not it will go low will depend on the state of the RD line. (From Z-80) Since write disabling is already provided for in the Arcade, there will be no disabling (No low outputs on control lines) unless it is a read.

#### **EXAMPLES:**

- 1. A RAM is located @ address range 8192 and an access is being made for a WR to this RAM. (The sw. is on for this device) CS 8 becomes low enabling data buss input to this RAM. (Output from 154 thru sw.) this causes the output of the 21 @ K4 to go low. This enables the RD signal thru the 125 (@D6) which doesn't matter anyway because RD is hi during a WR. Cassette disabling (To prevent data buss conflict) is being done by the Home Video hardware. If a RD is being made from this RAM, it will appear (low) on the CASEN line which will disable cassette ROM response. BÜZZOFF will also go low disabling data from MX buss. (Which would also cause conflicts.)

- 2. A RAM is located @ address range 16384 and the sw. is ON. CS 16 becomes low causing the 133s output to become hi. This is inverted by the 04 and will enable the 125 allowing the RD signal to appear as BUZZOFF. This disables MX buss return data on a RD from screen memory. If a WR is being done to this RAM (On the RAM board) it will trash your screen picture, but data will always be true to and from the memory board @ these addresses.

- 3. A WR is being done to RAM(s) located in the first two sockets. (This means you have installed a sw. to accomplish this, (In WR line) and that you must know what your doing since this is system ROM/Magic screen.)

- 4. An I.O. request is being made for either a RD or WR, to some I.O. port in I.O. ville. (Which doesn't mean Jacks beans because MREQ isn't low, and the RAM board is taking a nap.)

- 5. Power is disconnected from the RAM board. Some of the CS lines may be low causing system brain death on the data buss.

#### 64 KRAM COMPONENTS

74LS 154 - One of 16 decoder,

active low outputs,

binary (4) inputs.

Two ANDed low enables.

74LS 133 - 13 input NAND gate

74LS 125 - Quad tri-state buffer

w/seperate low enables.

74LS 21 - Dual 4 input AND gates.

74LS 04 - Hex inverter buffer.

(3 used in package)

MEMORY DEVICES / 2K x 8

TMM 2016-TC 5517 - Toshiba

MB 8128-MB 8416 - Fujitsu

HM 6116 - Hitachi

M 58725 - Mitsubishi

MK 4802 - Mostek

2716 - Any 5v. (only) 2K x 8 EPROM

2816 - Electrically Erasable/Programmable Romram

(EEPROM) - Mfr. - XICOR.

This device is more like a ROM than a RAM. When the power is shut down (Even without battery backup) the EEPROM will remember. However it is unnecessary to erase the contents with a U.V. lamp, or to have a programming unit to program it. (Such as the 2716 EPROM requires.) It can be programmed right where it sits in the same way normal RAM responds to reads, and writes. But since the write cycle is slow it cannot be used as normal RAM, activly changing its contents during program execution.

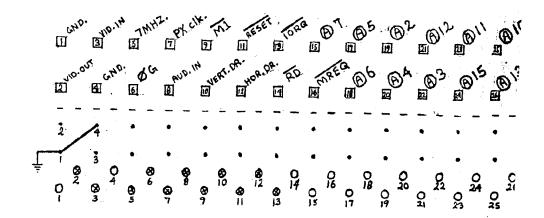

### 50 PIN BUSS SIGNALS

|    | z-80 s | ignals - *=Not used on 64K RAM board. P                                                                    | riority<br>Level |

|----|--------|------------------------------------------------------------------------------------------------------------|------------------|

|    | DO-D7  | Data Buss. (8-bits) These 8 lines are used for data                                                        |                  |

| ,  | A0-A15 | transfers to or from memory or 1.0. (Bidirectional) These 16 lines determine the location of an 8-bit      | <b>↓</b>         |

|    | RD     | number, to or from memory or 1.0. (Address Buss) Z-80 Output-Signals external devices that the pro-        |                  |

|    | WR     | z-80 Output-Signals external devices that the Z-80                                                         |                  |

|    |        | wants to write data to memory or 1.0.                                                                      |                  |

|    | MREQ   | Z-80 Output-Signals memory that the Z-80 is ready to memory Read or Write. (Address is now valid.)         |                  |

| *  | IORQ   | Z-80 Output-Signals 1.0. devices that it is ready for                                                      | r                |

|    |        | an i.0. address. (Lower half of address buss now has a valid 8-bit i.0. address. (Port #))                 |                  |

| *  | MT     | Z-80 Output-This signal is generated (Goes low) on every opcode fetch (Read) cycle.                        |                  |

| *  | INT    | Z-80 input-This signal causes the Z-80 to acknowledge                                                      |                  |

|    |        | an interrupt on its current program, if interrupts are enabled, and if BUSRQ and NMI are not active. If an | 3                |

|    |        | interrupt is acknowledged IORQ is also generated alor                                                      |                  |

|    |        | with MI to signal the interrupting device that it may place an interrupt vector on the data buss.          | 1                |

| *  | BUSRQ  | Z-80 Input-When the Z-80 recieves this signal it will                                                      | (.2)             |

|    |        | "float" its address, data, and other output lines so some other external device can use the buss.          |                  |

| *  | BUSAK  | Z-80 Output-Signals external requestor that the Z-80 is finished with its last-instruction and all of its  |                  |

|    |        | pins are now transparent. (Hi-impedence state)                                                             |                  |

| *  | RFSH   | Z-80 Output-Tells external dynamic memory that the address buss now has a 7 bit refresh address which      |                  |

|    |        | can be used during the current MREQ to refresh the                                                         |                  |

| *  | WAIT   | Z-80 Input-If this signal is activated the Z-80 will                                                       |                  |

|    |        | suspend operation after finishing its last instruction when WAIT goes Hi and it has                        | on •             |

|    |        | completed its last machine cycle. This allows slower                                                       | •                |

|    |        | devices to place valid data on the buss, or complete its response to an address.                           |                  |

| *  | HALT   | Z-80 Output-Becomes active during execution of the                                                         |                  |

|    |        | HALT instruction. (118) This indicates that the Z-80 is waiting for an interrupt to continue. The Z-80     |                  |

|    |        | executes NOPs (0) during HALT time to keep dynamic memory refreshed.                                       |                  |

| *  | NMI    | Z-80 Input-This signal will cause the Z-80 to jump to                                                      | o (3)            |

|    |        | location 102, which should be reserved for highest priority interrrupts. (Such as power failure mode)      |                  |

| .و | DECET  | NMI and BUSRQ will override the INT signal.                                                                | (1)              |

| ж  | RESET  | Z-80 Input-Resets program counter (PC), Refresh register (R), to 0, and also resets interrupt enable       | • •              |

|    |        | page (to 0), and mode. (to 0)                                                                              | ,                |

#### 50 PIN BUSS SIGNALS

These signals are unique to the Home Video system.

\* VID IN This can be used for overlaying a synchronized external picture. \* VID OUT Contains video and all standard subsignals for T.V. sets as generated by the Data Chip. \* 7 MHZ Clock signal (symmetrical) that drives the Data Chip. Clock signal (unsymmetrical every 1/60 sec. for 1/2 \* Ø G cycle of 7M) that drives the Z-80 1.0. and Address Chips. \* AUD IN Can be used to mix external sound into the R.F. modulator. Level in to get a volume of 15 = .78v. Level 1 = .14v. (Low impedence source - cuts out 1.0. audio.) To mix use series 12K resistor from external such as earphone output. Level in to get a volume equal to 15 = 1.8v. If this pin is used as an output the levels are; 15 = .68v. or .48 into 10K. 1=.13v. or .1v. into 10K load. (Measured @400Hz. out) This signal occurs once every 1/60 th of a second \* VERT DR as generated by the Data Chip. (To be used for sync. on external video mix.) This signal occurs once every scan line (3.185ms.) \* HOR DR as generated by the Data Chip. Also used to drive external video sync. If this line is brought low the cassette socket is CASEN deselected. Used to allow external memory respond at cassette range addresses. If this line is low external devices may use the addresses from 0 to 8191. The system ROM will be deselected. Disables microcyclor (Custom chips) to the Z-80 BUZZOFF only. Data may then be placed the Z-80 data buss to or from external memory or 1.0. (8 bits of address buss are still connected thru to Address chip.) This signal is used to insure Home Video data buss float while externals communicate with the Z-80. Also is used to allow address of external memory in the same addresses as onboard (Screen) memory. 16384 to 20479 Clock signal to sync. external pixels (?) (Occurs \* PX clk. once every pixel. - Unsymmetrical) (Ask Bally what they had in mind.)

#### MAGIC MEMORY

Magic memory is a term used to describe a situation where two seperate memory devices are utilizing the same memory addresses. (From the Z-80) That is, they are overlapped.

This must be a hardware configured item, and it is necessary to design in logic to prevent conflicts on the data and address buss.

Since the system ROM (0-8191) is only read, and never written to, the onboard hardware in the Home Video has been designed to use the range from 0-4095 to WRITE data to screen memory. This is done through the custom chip hardware which is also designed to support screen hardware from address 0. When a read is done in this range the data returns from system ROM. When a write is done in this range, data is written through the custom hardware to screen memory. So the screen memory can be considered write only memory in the address range from 0-4095.

Do not expect to have Magic Memory in areas other than those which exist in the Home Video hardware. That is, the custom chips in the Arcade are not wired together properly to address 16K (Hi-Res) Magic Memory. The write protect option for the lower 16K of memory was made available to support systems which have been configured for Hi-Res.

The Magic Memory being used must be write protected if it is located on the 64K RAM board. This is because when the switch(s) are turned on for that range the deselect logic on the RAM board will disable the Home Video (Thru CASEN/SYSEN...) and attempt to write to the memory devices located in those sockets. (Thus the missing jumper on the WR line in the lower 4K) If you intend to install RAM devices in the two lower left sockets, (0-4095) you must install the jumper to write to that memory, and then remove the jumper again so that the normal Magic functions to the screen will not wipe out your operating system located here.

As an example, you could, with switches CSO and CS2 in the OFF position, block load the existing system ROM contents (0-4095) to a higher block of memory. (Somewhere) Now with two RAMs installed in those sockets you could flip switches CSO & CS2 to their ON position, add the jumper, and block load it back down. (After modifying (?) A.Y.O.R.) The jumper should then be removed so the system can do its normal Magic Screen writes without destroying your operating system.

By putting the switch in where the 16K (0-16K) Hi-Res Magic write jumper is now, you can write protect the memory from 16383 to 0. (Don't forget that this includes the Cartridge Range, and you will not be able to Write to RAM located here without turning the sw. ON)

This board is not designed for cartridge bootleggers, and does not come with deluxe copy features, such as a switch to change memory locations. (Anyway, if you know how you can)

In ither words - if you have memory in any sockets which are currently being used by some external memory, (Such as Cartridge, or Second Expand memory) those CS switches must be in the OFF poition. This means that any memory device plugged into these sockets (@ these locations) cannot be read, or written to while the external memory is connected.

Having switches in the ON position for locations which are both external and 64K memory board, will cause catastrophic conflicts on the buss. This will not cause electrical damage in most cases. However the user should beware of any conflicts of memory overlapping. Of course if this happens the total system may become inoperative. If there are strange 1.0. devices, (Or other externals) connected we cannot guarantee components will not be stressed or even destroyed. (It is possible to create a situation that will not cause the system to become inoperative while still having overlapping memory locations...So look before leaping.)

#### INTERGALACTIC POLITICS

Software and hardware for memory bank selecting is not available at this time. "It is possible to AUTOMATIC memory bank selecting in machine language for toggling from one bank to another through the software." Invent your own ranges for magic memory?... For instance then plug on some external memory (such as the viper) and locating it say from the 0-16K range, toggle your magic function to create any combination of read write functions between the two overlapping ranges. This couldbe useful to create a write only memory that could be storing information which could read back through the use of one of your software (magic) routines. This also opens up the possibility for an external video controller or character generator system. This could be controlled through dedicated I.O. functions using the 16 bits of the Z-80s BC register. If you think this may mean a Hi-Res. graphics system hookup ... you are correct.

Further dedicated I.O. functions could also be added, such as DMA, Disk Controller and driver software, and RS-232 serial with a programmable baudrate. Other possible hardware configured items (Allowing the Z-80 to be doing something else) are; Tape drive controller - Seperate 300 baud telephone modem

Separate 1800 to 2700 baud tape (cassette) input-output.

Mathematical function unit - Counter/timer circuit

Z-80 PlO (General parallel 1.0.) to take c of just

bout aything else such as light show controller. BSR controller.

about aything else, such as light show controller, BSR controller, ROM programmer, etc..etc.

So you can see that by leaving the hardware open for further expansion by providing the second expand jack, and making sure the deselection logic is done properly, it has been made possible ....

(to back page)

to have something in every one of the 32 sockets and be able to use it. (Along with something in the pseudo-same address range externally) Basically this is similar to the method that will be used to access floppy disk. However if disk is implemented it is more logical to use the memory on the 64KRAM for a high speed/high capacity buffer. (Address ranges, or memory blocks are then selected through 1.0.functions.)

"A scheme for overlapping another 4K of memory in the screen area could also be implemented to create a software to hardware controlled memory swap..." At this point the DMA action to the actual internal screen RAM (Being scanned by the address chip) simply becomes a software block load from one range to another. (This would provide a good means for getting a picture in from disk for creating,..would you believe cartoons.) You would be reading it from say 16384 (RAM board) and writing it to 0. (Magic screen memory)

Sorry, you cannot change screen RAM (Internal-What you're watching) 60 times a second, with the software driven by the Z-80. The Z-80 has a limited operating speed, and is slowed down even more when reading or writing to screen RAM, because it has to do everything 3 times. (The good old multiplexed buss system.) The operating speed cannot be increased (Contrary to popular belief in the Z-80B) because the clock that drives the Z-80 comes from the Data Chip. This has a set speed for producing the video, and the Z-80 clock, and microcyclor work hand in hand to insure proper memory/device operation in all directions.

If you think you have a way to switch clocks on the Z-80 only in certain address ranges... Go for it!! Let us know if you would. (Or did!) WAIT states are also something to watch...But watch it! (Or do you have a dual trace?)

Further information on what this is all about may be freely obtained by calling us. We know what to expect if hardware kludges are to be added to the Home Video. (However we are not interested in providing any hack attachments ourselves.) Whereas, we are lookin for, and have found ways of easily expanding the unit as it stands from the 50 pin expand jack.

1.0. capabilties, and software is the main article for further functionality and speed. Ease of usage is also being taken into consideration. If you have any ideas or suggestions along those lines please drop us one.

CONNECTIONS MADE PHYSICALLY

BETWEEN 2'nd exp. & HEADER

50 PIN # INSIDE

=CONNECTIONS TO HOLES

E

D