# 30 CUSTOMIZED MICROPROCESSOR PROJECTS

DELTON T. HORN

# 30 CUSTOMIZED MICROPROCESSOR PROJECTS

**DELTON T. HORN**

#### FIRST EDITION

#### SECOND PRINTING

Printed in the United States of America

Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein.

Copyright © 1986 by TAB BOOKS Inc.

Library of Congress Cataloging in Publication Data

Horn, Delton T.

30 customized microprocessor projects.

Includes index.

1. Microprocessors—Amateurs' manuals. I. Title. II. Title: Thirty customized microprocessor projects. TK9969.H67 1986 621.391'6 86-5855 ISBN 0-8306-0705-6 ISBN 0-8306-2705-7 (pbk.)

Questions regarding the content of this book should be addressed to:

Reader Inquiry Branch Editorial Department TAB BOOKS Inc. P.O. Box 40 Blue Ridge Summit, PA 17214

### **Contents**

|   | Introduction                                                                                                                                                                                               | v   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | List of Projects                                                                                                                                                                                           | vi  |

|   | Section I The Basics                                                                                                                                                                                       | . 1 |

| 1 | The Basics of Circuit Design  Semiconductors—Ohm's Law—Power—Combining Component Values—Kirchhoff's Laws—Ac Values—Resistance in Ac Circuits—Trigonometric Functions—Logarithms—Laplace Transforms—Summary | 3   |

| 2 | Digital Basics  Number Systems—BCD—The Gate—The Multivibrator— Counters—Shift Registers—Multiplexers and Demultiplexers— Display Drivers—Bilateral Switches—Three-State Logic                              | 67  |

| 3 | The CPU Commands and Data—Components of a Computer—The Z80                                                                                                                                                 | 95  |

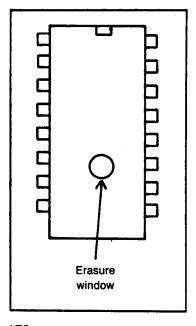

| 4 | Semiconductor Memory RAM—ROM—PROM—EPROM—Measuring Memory Size—Other Memory Devices                                                                                                                         | 113 |

| 5 | Interfacing Memory Mapped I/O—Direct I/O—Z80 Interface Timing—Bus Interface Circuitry—Interfacing Analog Signals                                                                                           | 125 |

|   |                                                                                                                                                                                                            |     |

|    | Section II<br>Projects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 151 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6  | CPU Breadboard  Components of the System—Power Supply—The CPU—Clock— Memory—Hexadecimal Keypad—LED Data Read-Out—The Breadboard System                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 153 |

| 7  | EPROM Programmer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 173 |

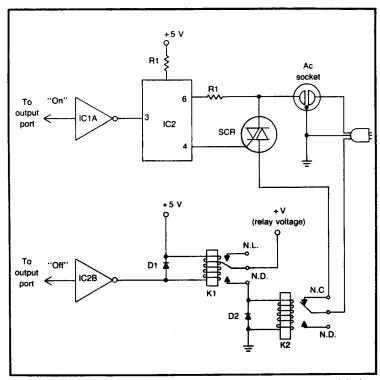

| 8  | Timer/Automation Systems Ac Controller—Addressing—Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 181 |

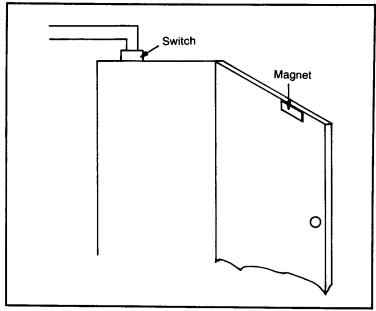

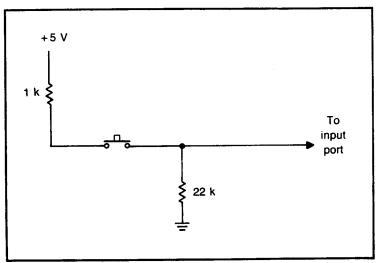

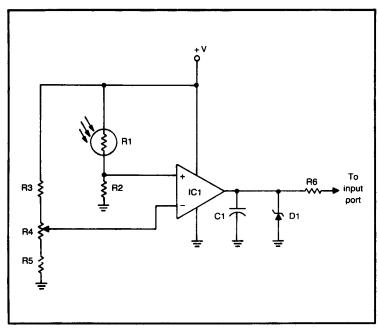

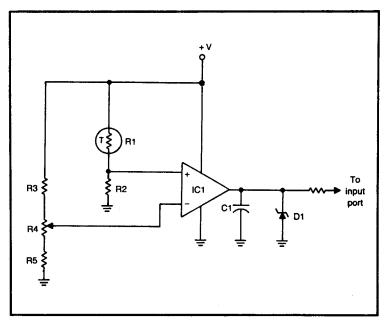

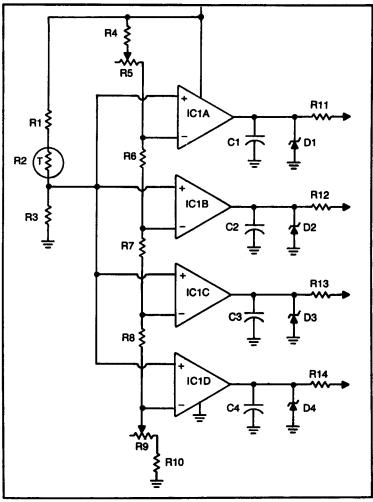

| 9  | Security Systems  Burglar Fooler—Door/Window Switches—Broken Beam Detectors—Heat Sensor—Smoke Detectors—Output Alarms and Indicators—Reset—Software                                                                                                                                                                                                                                                                                                                                                                                                                                               | 187 |

| 10 | Test Equipment  D/A and A/D Converters—Voltmeter—Ohmmeter—Capacitance  Meter—Semiconductor Tester—Digital Circuit Tests—Computerized Oscilloscope Functions                                                                                                                                                                                                                                                                                                                                                                                                                                       | 205 |

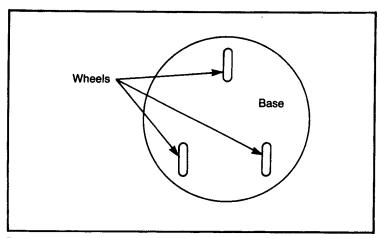

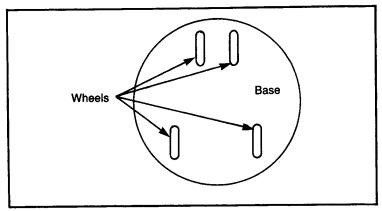

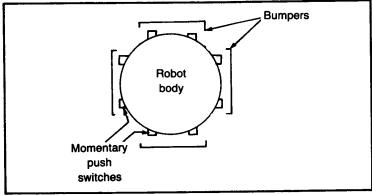

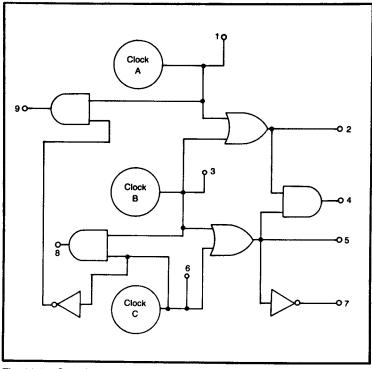

| 11 | Robots Basic Mobility—Sensors—Frills—For More Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 227 |

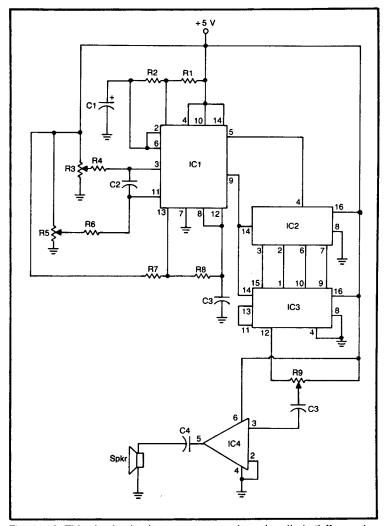

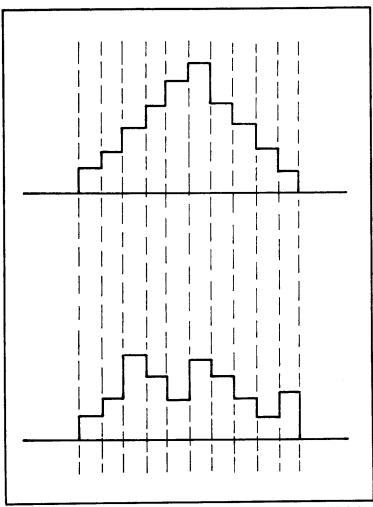

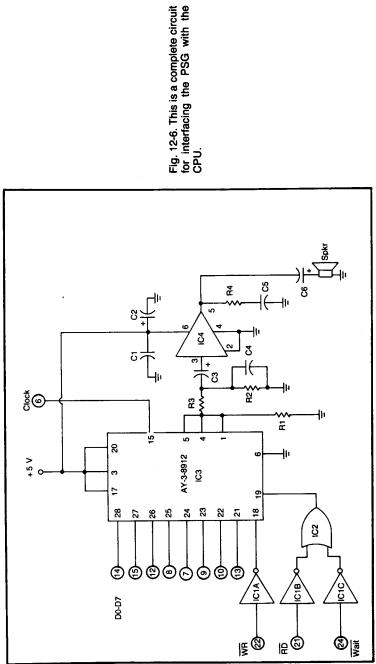

| 12 | <b>Sound Synthesis</b> Interfacing with an Analog Synthesizer—Direct Digital Synthesis—PSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 243 |

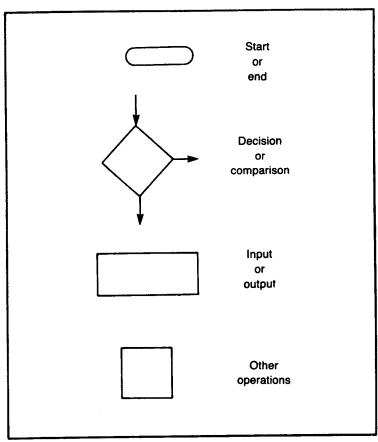

| 13 | Programming Machine Language and Assembly Language—Z80 Commands— Flowcharts—Building a Library of Software Routines—Final Suggestions                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 257 |

|    | Appendix A The Z80 Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 263 |

|    | Appendix B Hexadecimal Codes for the Z80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 283 |

|    | Appendix C Sample Computer Programs  How to Enter the Programs—Directions for Using the EPROM Programmer—Program 1/Sample Software for Project 9 (Ac Controller)—Program 2/Sample Software for Project 10 (Intrusion Detector)—Program 3/Sample Software for Project 14 (Multilevel Temperature Detector)—Program 4/Sample Software for Project 19 (Ohmmeter)—Program 5/Sample Software for the IC Tester Circuit—Program 6/Sample Software for the Motor Control Circuit—Program 7/Sample Software for the Sound Detector Circuit—Program 8/Sample Software for the Programmable Sound Generator | 291 |

|    | Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 298 |

#### Introduction

VERYONE KNOWS THAT COMPUTERS ARE POWERFUL DEvices that can be used for many tasks. Sometimes, however, it is difficult to justify tying up a complete computer system to perform two or three specific tasks. The solution is to build a special purpose computer around a CPU (Central Processing Unit) IC.

This book will help the intermediate to advanced electronics experimenter design and build custom dedicated CPU projects. The emphasis will be on customization for individual applications. The reader is not limited to the circuitry the author considers useful.

The various projects in this book are designed for maximum interchangeability to allow the experimenter to build almost any customized system. The first half of the book discusses basic principles of circuit design and computer systems. The second half of the book describes the projects.

## **List of Projects**

| 1  | System Power Supply                | Chapter 6  |

|----|------------------------------------|------------|

| 2  | System Clock                       | Chapter 6  |

| 3  | On-Board RAM                       | Chapter 6  |

| 4  | Hexadecimal Keypad                 | Chapter 6  |

| 5  | Memory Stepper                     | Chapter 6  |

| 6  | Two-Digit Display                  | Chapter 6  |

| 7  | EPROM Programmer                   | Chapter 7  |

| 8  | Supplemental Power Supply          | Chapter 7  |

| 9  | Ac Controller                      | Chapter 8  |

| 10 | Normally-Open Intrusion Detector   | Chapter 9  |

| 11 | Normally-Closed Intrusion Detector | Chapter 9  |

| 12 | Light Sensor for Broken Beam De-   |            |

|    | tector                             | Chapter 9  |

| 13 | Simple Temperature Detector        | Chapter 9  |

| 14 | MultiLevel Temperature Detector    | Chapter 9  |

| 15 | Alarm Signaller                    | Chapter 9  |

| 16 | Alarm Delay Circuit                | Chapter 9  |

| 17 | Practical D/A Converter            | Chapter 10 |

| 18 | Practical A/D Converter            | Chapter 10 |

| 19 | Ohmmeter                           | Chapter 10 |

| 20 | Capacitance Meter                  | Chapter 10 |

| 21 | Semiconductor Tester               | Chapter 10 |

| 22 | Four-Bit Digital Probe             | Chapter 10 |

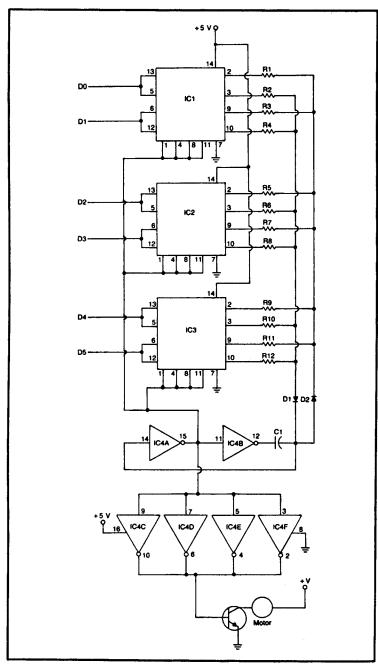

| 23 | IC Tester                          | Chapter 10 |

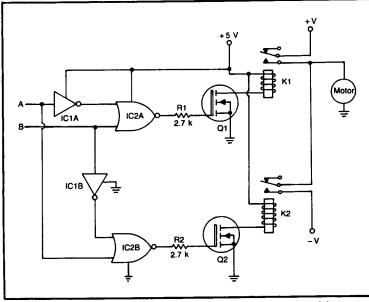

| 24 | Motor Forward/Reverse Control | Chapter 11 |

|----|-------------------------------|------------|

| 25 | Motor Control With Steering   | Chapter 11 |

| 26 | Motor Speed Controller        | Chapter 11 |

| 27 | Photodetector Circuit         | Chapter 11 |

| 28 | Sound Detector                | Chapter 11 |

| 29 | "Robot Sound" Generator       | Chapter 11 |

| 30 | Programmable Sound Generator  | Chapter 12 |

# Section I The Basics

# Chapter 1

### The Basics of Circuit Design

This Chapter is not intended to teach the novice how to design electronic circuits. It is intended strictly as a convenient refresher for intermediate and advanced experimenters. If you do not have any prior experience in this area, I strongly recommend that you read a text or two on general circuit design before tackling the projects described in this volume. The principles of electronic design are covered in some detail in my earlier works, Transistor Circuit Design—with Experiments (TAB book 1875) and Designing IC Circuits . . . with Experiments (TAB book 1925).

#### **SEMICONDUCTORS**

All matter, as you should already know, is made of atoms. The primary components of an atom are protrons (positively charged particles), electrons (negatively charged particles), and neutrons (neutral particles). The protrons and the neutrons are clumped together in the nucleus. The electrons circle the nucleus like the planets around the sun.

Ordinarily, the number of electrons exactly equals the number of protrons. The negative charges cancel out the positive charges, and the atom as a whole is electrically neutral.

Some elements can accept extra electrons (gaining a negative charge), and/or give up a few of their own (gaining a positive charge). These materials allow electrical current to pass through them fairly easily. They are known as *conductors*. Most (but not

all) conductors are metallic. Silver and copper are typical conductors.

In other materials, it is very difficult to change the number of electrons. These materials tend to block the flow of electrical current. They are called *insulators*. Typical insulators are rubber and glass.

Modern electronics depends heavily on a third class of materials, mid-way between conductors and insulators. These materials are called *semiconductors*, and usually are in crystalline form. The most commonly used semiconductors are germanium and silicon.

By itself a pure semiconductor material isn't good for very much. It can be used to make a fair resistor, and that's about it. But, if a small amount of an impurity (a second, related element) is added, the semiconductor begins to exhibit some special properties. The amount of impurity is very minute—often as small as one part in 10,000,000.

Let's consider what happens if a few arsenic atoms are added to a slab of germanium. The arsenic atoms will try to act like germanium and join in the crystalline structure. But arsenic has more electrons than germanium. Once the spaces in the crystal structure have been filled in, there are still a few electrons left over. Because these excess electrons are only loosely bond to the arsenic atoms, they will move about the entire crystal, "looking" for a place to settle. Since they can't find a convenient niche, they will continue to roam.

The loose electrons wandering around within our doped germanium crystal represent a small wandering local negative charge. But the overall charge of the crystal as a whole is neutral, because the number of electrons exactly equals the number of protons.

If an electrical voltage is placed across the crystal, the loose electrons will be drawn to the positive terminal, because there is nothing much to hold them in place within the crystal. So they leave the crystal altogether for the positive terminal of the voltage source.

Now, there are more protons in the crystal than electrons. The crystal, as a whole, has a positive charge. It will attract electrons from the negative terminal of the voltage source. This neutralizes the crystal's electrical charge, but the new electrons still can't find a place to "sit" so they are drawn out of the crystal by the positive side of the voltage source. This continues as long as the voltage source is applied to the crystal.

The semiconductor material is conducting electricity, but in a somewhat different manner than ordinary conductors. We will examine the significance of this shortly.

Using arsenic as an impurity adds extra electrons to the crystalline structure. Therefore, arsenic is called a *donor impurity*. Other donor impurities are antimony, bismuth, and phosphorous. The result of adding a donor impurity is an n-type semiconductor.

Alternatively, we could dope the crystal with an impurity that has too few electrons to fill the crystalline structure. In other words, there are several *holes* where electrons would fit if they were available. The surrounding electrons will keep trying to fill up these holes. They sort of play "musical chairs", but it doesn't accomplish much, since there are always more holes than electrons. In a real sense, the holes move around within the crystal, just as the loose electrons did in the earlier version. We now have loose holes. A minute localized positive charge drifts about within the crystal.

Once again, if a voltage source is applied to the semiconductor crystal, current will flow. Electrons will be pulled in from the negative terminal to fill the excess holes. This gives the crystal, as a whole, a negative electrical charge, which is tapped off by the positive terminal.

Impurities with too few electrons are called *acceptor impurities*. Typical elements used as acceptor impurities are aluminum, boron, and gallium. A semiconductor slab doped with an acceptor impurity is called a *p-type semiconductor*.

#### The Pn Junction

Neither n-type nor p-type semiconductors are particularly exciting or interesting by themselves. Their important properties show up when a junction is formed between the two different types of semiconductors.

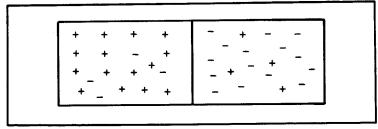

It is important to remember that both n-type and p-type semiconductors have both electrons and holes flowing through them. The difference is in which type of carrier is in the majority. In an n-type semiconductor, electrons are the majority carriers and holes are the minority carriers. In a p-type semiconductor, this is reversed. When no voltage is applied to a pn junction, the carriers (electrons and holes) are more or less randomly distributed, as illustrated in Fig. 1-1.

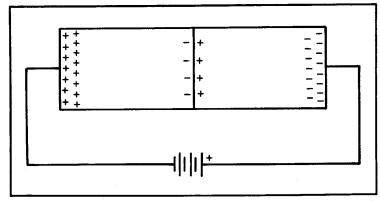

In Fig. 1-2 we see the result of applying a voltage across the pn junction with the positive terminal connected to the n-type side,

Fig. 1-1. Carriers are randomly distributed around a pn junction when no voltage is applied.

and the negative terminal connected to the p-type side. The excess electrons are drawn towards the positive terminal on the n-side of the junction. Similarly, the excess holes move towards the negative terminal on the p-side.

Virtually all the loose carriers are drawn to the ends of the semiconductor slab. There are almost no loose electrons or holes near the junction at the middle. Essentially, the junction is the same as if it had never been doped with any impurity. It acts as a fair insulator. The result is that almost no current will flow through the junction. It behaves almost like an open circuit. (There will be a very small amount of current flow due to the minority carriers but this is so small that we can reasonably ignore it here.)

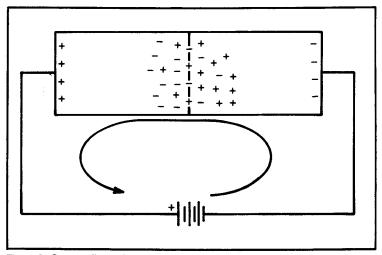

Now, let's see what happens when the polarity is reversed, as shown in Fig. 1-3. The negative terminal is connected to the n-side and the positive terminal is connected to the p-side. Since like charges repel, the loose electrons in the n-type side are forced towards the junction. Similarly, the loose holes in the p-side are also driven towards the junction. The loose electrons and holes have

Fig. 1-2. Almost no carriers can cross the pn junction when it is reverse biased.

Fig. 1-3. Current flows through a pn junction when it is forward biased.

enough energy to jump across the junction and neutralize each other. The loose electrons fill the loose holes.

The p-type semiconductor has a negative charge because extra electrons from the n-side have filled its holes. Similarly, the ntype semiconductor has a positive charge because it has lost some if its electrons.

The positive charge on the n-side draws more electrons from the negative terminal of the power source, while the excess electrons flow from the negatively charged p-type material to the positive voltage terminal. This means the n-side again has loose electrons and the p-side again has loose holes. These are forced through the junction, and the process continues.

In other words, current can flow through a pn junction in only one direction. If current is applied in the opposite direction, it is blocked. A pn junction serves as a semiconductor diode.

#### The Bipolar Transistor

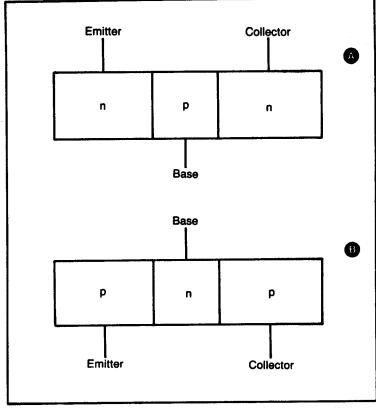

As useful as the diode is, we can do even more if we have a pair of back-to-back pn junctions, as shown in Fig. 1-4. In effect we have a semiconductor sandwich. This device is called a transistor. There are many different types of transistors. The simplest (which is shown here) is the *bipolar transistor*.

There are two possible combinations for a bipolar transistor. There could be two slabs of n-type material on either side of a thinner slab of p-type material, as shown in Fig. 1-4A. This is called

Fig. 1-4. A transistor is basically a pair of back-to-back pn junctions. (A—npn, B—pnp.)

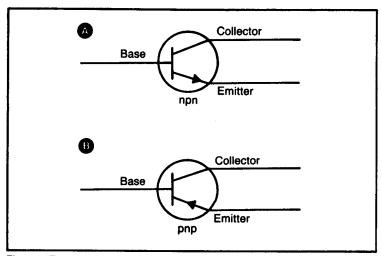

a npn transistor. Alternatively, we could have a central n-type slab surrounding by p-type slabs, as illustrated in Fig. 1-4B. This is called a pnp transistor. The schematic symbols for these two devices are shown in Fig. 1-5. The three leads have special names—the *emitter*, the *base*, and the *collector*.

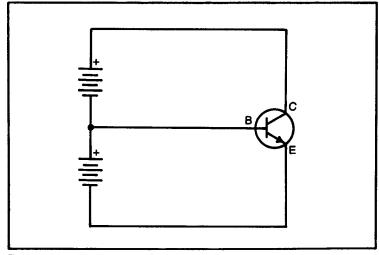

In the following discussion, we will discuss just the npn transistor. The principles are the same except for the electrons and holes, and all circuit polarities are reversed. The transistor permits signal amplification because the collector current is dependent on the base to emitter current.

#### Alpha

The correct relative polarities (biasing) for an npn transistor are illustrated in Fig. 1-6. When biased in this manner, more emit-

Fig. 1-5. The three leads of a transistor are easy to identify in the schematic symbol. (A—npn, B—pnp.)

ter current  $(I_e)$  will flow through the transistor than either base current  $(I_b)$  or collector current  $(I_c)$ . In fact, ignoring a few minor losses, the emitter current is essentially equal to the sum of the other two currents. That is:

$$I_e = I_b + I_c$$

Fig. 1-6. This is a correctly biased npn transistor.

Let's assume the following currents flowing through a hypothetical transistor:

$$I_e = 20 \text{ mA}$$

$I_b = 0.7 \text{ mA}$

$I_c = 19.3 \text{ mA}$

Notice that these values fit into the formula given above:

$$20 = 0.7 + 19.3$$

The ratio of the collector current to the emitter current is the *alpha* of the transistor. The symbol for alpha is  $\alpha$ , and the formula is:

$$\alpha = I_c/I_e$$

The alpha is a constant for any given transistor. If the emitter current changes for any reason, the collector current will change accordingly. The alpha will always be less than 1. This is because the collector current must, by definition, must be smaller than the emitter current:

$$I_c = I_b - I_b$$

Ordinarily, the base current  $(I_b)$  will be very small, so the collector current  $(I_c)$  will be close to the emitter current  $(I_c)$ . This means that normally the alpha of a transistor will be close to, but slightly less than 1.

For our hypothetical transistor, the alpha is:

$$\alpha = I_a/I_a = 19.3/20 = 0.965$$

This is a fairly typical value.

#### Beta

Another useful relationship among transistor currents is the ratio of the collector current to the base current. This ratio is called beta, and its symbol is  $\beta$ . The formula for beta is:

$$\beta = I_c/I_b$$

Because the base current is always very small, as compared

to the collector and emitter currents, beta will normally have a fairly high value. Typical beta values for silicon transistors range from about 10 to about 1000.

The value of beta for our hypothetical transistor works out to:

$$\beta = I_c/I_b = 19.3/0.7 = 27.57$$

The value of beta can be derived from the value of alpha, by using this formula:

$$\beta = \alpha/(\alpha - 1)$$

Similarly, if we know the value of beta we can easily find the value of alpha by using this equation:

$$\alpha = \beta/(\beta + 1)$$

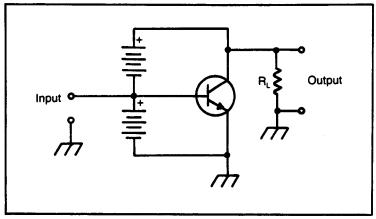

#### The Common-Emitter Circuit

There are three basic transistor amplifier circuits. In each of these, one of the transistor's three leads is referenced to the circuit's ground, or common point.

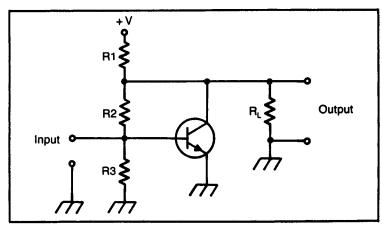

The common-emitter circuit illustrated in Fig. 1-7, is probably the most widely used. As the name suggests, the emitter is used as the common element. It is common to both the input and output circuits. The input signal is applied to the circuit across the base

Fig. 1-7. The common-emitter circuit is probably the most commonly used transistor circuit.

and the emitter, while the output signal is tapped off across the collector and the emitter.

In most practical circuits, separate power supplies usually aren't used for the base (input) and collector (output) circuits. Instead, a common voltage source is used for both, as shown in Fig. 1-8. Resistors R2 and R3 drop the voltage down to the necessary level.

The output of a transistor amplifier is in current form. In the common-emitter amplifier, the output signal is the collector current ( $I_c$ ). Several factors determine the level of this current, including, the transistor's beta, the base supply voltage (E1), the base resistor ( $R_b$ ), the emitter resistor ( $R_c$ ), and the internal voltage drop across the emitter-base junction. This voltage drop is usually about 0.7 volt for silicon transistors. Germanium transistors have a smaller voltage drop across the junction (typically about 0.2 to 0.3 volt).

The approximate value of the collector current  $(I_c)$  can be found with this formula. It is not exact, but it will be close enough for most purposes:

$$I_c = \frac{V_b - V_{be}}{\frac{R_b}{\beta} + R_e}$$

where  $V_b$  is the input signal voltage applied to the base,  $V_{be}$  is the voltage drop across the base-emitter junction,  $R_b$  is the base resis-

Fig. 1-8. A single power supply is usually employed for practical common-emitter circuits.

Fig. 1-9. This is the basic common-base transistor circuit.

tor,  $\beta$  is the beta, and  $R_e$  is the emitter resistor.

Let's say we are using a silicon transistor with a beta of 100. Since this is a silicon device.  $V_{be}$  will be 0.7 volt. In our sample circuit we will assign a value of 5000 ohms to  $R_{b}$  and 300 ohms to  $R_{e}$ . Plugging these values into the equation, we get:

$$I_{c} = V_{b} - 0.7/(5000/100) + 300$$

$$= V_{b} - 0.7/50 + 300$$

$$= V_{b} - 0.7/350$$

In a circuit of this type, the values of  $V_{be}$ ,  $R_b$ ,  $R_e$ , and  $\beta$  are constants, so the collector current  $(I_c)$  is controlled by the voltage being fed to the base of the transistor  $(V_b)$ .

Current gain, voltage gain, and power gain are all high for the common-emitter amplifier. The output signal is inverted, or 180° out-of-phase with the input signal.

The input impedance is low and the output impedance is high.

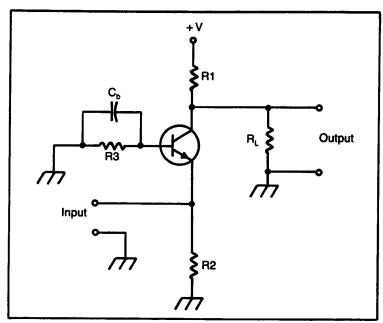

#### The Common-Base Circuit

In the common-base circuit, shown in Fig. 1-9, the input is applied across the emitter and the base, and the output is taken from

the collector and the base. In this configuration, the signal gain is defined by the ratio of the collector current  $(I_c)$  to the emitter current  $(I_c)$ :

$$Gain = I_c/I_e$$

This is the same as the value for alpha. Therefore, the current gain must always be less than unity, but this circuit is capable of medium voltage gain, and high power gain. The output signal is in-phase with the input signal.

The input impedance is very low, and the output impedance is very high. This circuit is often used for impedance matching applications.

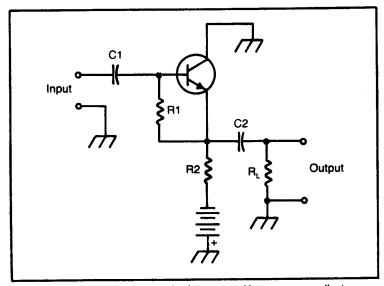

#### The Common-Collector Circuit

The third configuration for a transistor circuit is the commoncollector amplifier, which is shown in Fig. 1-10. In this circuit, the input signal is fed across the base and the collector, and the output is tapped off across the emitter and the collector.

Notice that the positive terminal of the voltage source is grounded so all operating voltages within the circuit must be negative. The emitter is normally held at the most negative level.

Fig. 1-10. Transistor circuits can also be arranged in a common-collector configuration.

Fig. 1-11. A UJT is a transistor with a single pn junction.

The voltage gain for a common-collector amplifier is always less than 1 (below unity). The current gain is fairly high, but the power gain is low. This configuration actually does not make a very good amplifier.

The input impedance is moderately high, and the output impedance is low, so the common-collector circuit is often used for impedance matching in multiple-stage transistor circuits. The output signal is in-phase with the input signal.

#### **Other Transistor Types**

Generally, when we say "transistor" we are referring to the bipolar transistor, as described in the last few pages. Bipolar transistors are certainly the most common type of transistors. But there are other important types of transistors, each with their own unique internal structure.

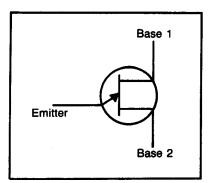

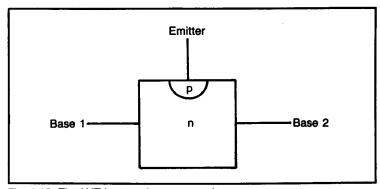

The unijunction transistor, or UJT, has just a single pn junction. Its schematic symbol is shown in Fig. 1-11. The internal struc-

Fig. 1-12. The UJT has two base connections.

Fig. 1-13. This is a simplified equivalent circuit for a n-type UJT.

ture of the UJT is illustrated in Fig. 1-12. Notice that there are two base connections, on either side of the larger n-type section.

The n-section acts as a voltage divider resistor pair, with a diode (the pn junction) connected to the common end of the two resistances. A simplified equivalent circuit for an n-type UJT is shown in Fig. 1-13.

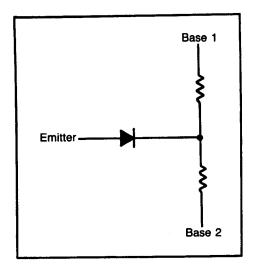

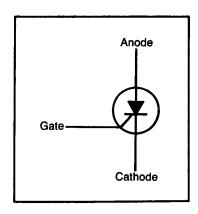

Closely related to the UJT is the PUT, or *Programmable Unijunction Transistor*. The schematic symbol for this device is shown in Fig. 1-14. Its internal structure is shown in Fig. 1-15. The PUT has three leads, labeled A (anode), C (cathode), and G (gate).

A voltage is placed across the anode and the cathode, with the anode positive with respect to the cathode. No current will flow

Fig. 1-14. A variation on the UJT is the PUT.

Fig. 1-15. The basic internal structure of the PUT.

between the anode and cathode until a negative (with respect to the anode) pulse is applied to the gate.

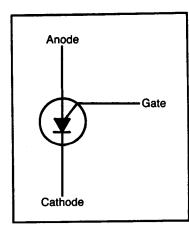

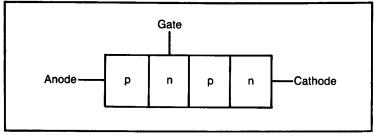

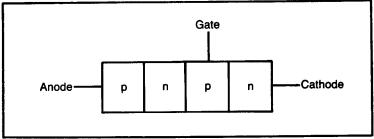

A silicon-controlled rectifier, or SCR, is essentially an electrically switched diode. It is very similar to the PUT. The schematic symbol for a SCR is illustrated in Fig. 1-16. As Fig. 1-17 illustrates, the main difference in the internal structure between the SCR and the PUT is the location of the Gate connection.

If a voltage is applied between the anode (+) and the cathode (-), and the gate is grounded (0 volts), no current will flow, even though the pseudo-diode is forward biased.

If an increasingly positive voltage is applied to the gate terminal, it will eventually reach a specific trigger voltage (which is dependent on the individual SCR used). Now, current can flow from the cathode to the anode, as if through an ordinary forward-biased diode.

If the gate voltage is now removed, current will continue to flow through the device. This current will continue to flow until the voltage between the anode and the cathode is interrupted.

Perhaps the second most commonly used type of transistor is

Fig. 1-16. A SCR is essentially an electrically switched diode.

Fig. 1-17. The internal structure of the SCR is similar to that of the PUT, except for the location of the gate connection.

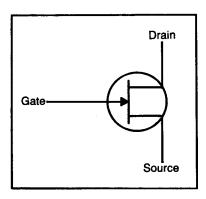

the FET, or *field-effect transistor*. The schematic symbol for the FET is shown in Fig. 1-18.

Many transistor circuits are variations on older vacuum tube circuits. There are many similarities in operation between transistors and vacuum tubes. However, the operation of a standard bipolar transistor doesn't quite correspond to that of a vacuum tube. Some transistor circuits won't work as well as vacuum tube circuits.

Does this mean we have to forego modern semiconductor technology and revert to bulky, expensive, and hot vacuum tubes? Not at all. The FET is a semiconductor device that can closely mimic the operation of a vacuum tube. In addition, it is capable of several unique tricks of its own.

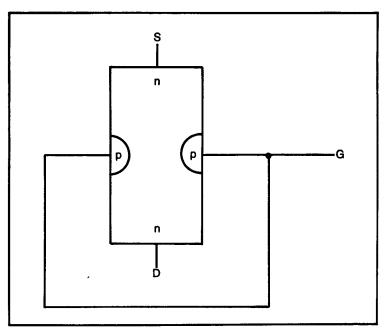

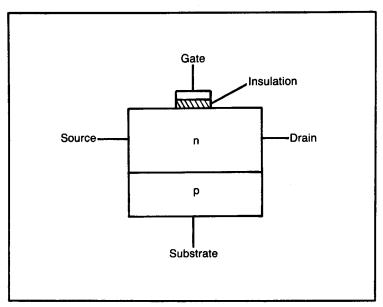

The basic internal structure of a FET is illustrated in Fig. 1-19. Notice that there are again three leads. In this case they are labelled S (source), D (drain), and G (gate).

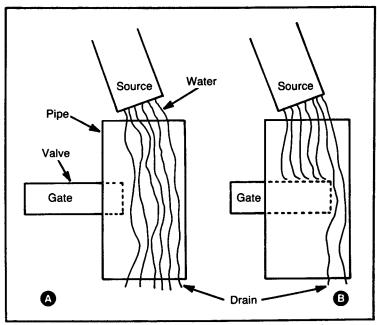

To get a general idea of how a FET works, consider the mechanical water system illustrated in Fig. 1-20. When the valve (gate) is fully opened, as in Fig. 1-20A, the water can flow through the pipe, from its source to where it can drain out. If, on the other

Fig. 1-18. FETs are almost as popular today as simple bipolar transistors.

Fig. 1-19. Simplified diagram of a FET's internal structure.

Fig. 1-20. A FET can be thought of as similar to a mechanical water pipe system.

hand, the valve is partially closed, as in Fig. 1-20B, the amount of water that can flow through the pipe is limited. Less water comes out of the drain. If the valve is completely closed off, no water at all will be able to flow through the pipe. Nothing will come out of the drain. In the same way, the gate terminal of a FET controls the amount of electrical current that can flow from the source terminal to the drain terminal.

The basic FET described above is more properly called a *junction field-effect transistor* (JFET). This is not the only type of FET available. Another type does not have an actual pn junction at all. These devices are known generically as *insulated gate field-effect transistors*, or IGFETs. As the name clearly states, the gate is insulated from the channel.

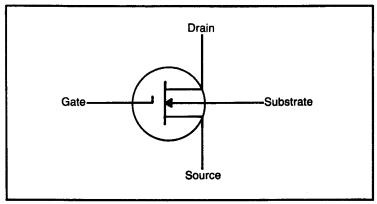

The most common way of doing this is by using a thin slice of metal as the gate (rather than a slab of semiconductor crystal). This metal is oxidized on the side that is placed against the semiconductor channel. This insulates the gate from the semiconductor because metal oxide is a very poor conductor. When a metal oxide gate is used, the IGFET is often called a MOSFET, or *metal-oxide-silicon field-effect transistor*. The basic internal structure of a MOSFET is illustrated in Fig. 1-21. The schematic symbol is shown in Fig. 1-22.

Fig. 1-21. A variation on the FET is the MOSFET.

Fig. 1-22. The schematic symbol used to represent a MOSFET.

#### The IC

The transistor, and its relatives, made a lot of electronic applications practical that would not have been feasible using vacuum tubes. The transistor went a long way towards reducing the size and cost of electronic circuitry, but the industry still wasn't satisfied. Semiconductor techniques were improved and miniaturization was increased, leading to the development of the *integrated circuit*, of IC. Multiple transistors, and other components (such as resistors and capacitors) are etched onto a single slab of semiconductor material about the size of your thumbnail. The earliest ICs replaced just a handful of discrete components, which was impressive in and of itself, but modern ICs can be the equivalent of hundreds or even thousands of discrete components. It is the IC that makes the microcomputer possible.

In this book we will be concerned primarily with digital ICs. These devices will be discussed in more detail in Chapter 2.

#### **OHM'S LAW**

Anyone working with circuit design needs at least a basic grasp of a number of mathematical formulas. Fortunately, these aren't really as hard to use as you might suspect.

The most important and widely used formula in electronics work is also the simplest. You can't possibly do any serious work in the electronics field without knowing Ohm's law.

Ohm's law is a method for comparing the current, voltage, and resistance in a circuit. The basic formula states that the voltage (in volts) (E) equals the product of the current (in amperes) (I) mul-

tiplied by the resistance (in ohms) (R). That is:

$$E = IR$$

This formula can be easily rearranged to solve for any of the three variables involved. For example, to find the current when you know the voltage, and the resistance, use this formula:

$$I = E/R$$

Similarly, if you know the current and the voltage, you can find the resistance by using this equation:

$$R = E/I$$

Let's consider a few simple examples. If we have 20 mA (0.02 amp) across a 100-ohm resistor, the voltage drop will be equal to:

$$E = IR = 0.02 \times 100 = 2 \text{ volts}$$

Now, let's say we have 9 volts applied across a 2.2 k $\Omega$  (2200 ohm) resistor. The current flow works out to:

$$I = E/R = 9/2200 = 0.0041 \text{ amp} = 4.1 \text{ mA}$$

If we need a 15-volt drop and a current flow of 35 mA (0.035 amp), what size resistor do we need? The required resistance can be easily found using the Ohm's law formula:

$$R = E/I = 15/0.035 = 43$$

ohms

#### **POWER**

The fourth most important parameter in electrical circuits (after voltage, current, and resistance) is the amount of power consumed. The standard unit for power is the *watt*. Power, in watts, equals the product of the voltage (in volts) multiplied by the current (in amps). That is:

$$P = EI$$

As a practical example, let's say we have 250 mA (0.25 amp) current flowing in a 10-volt circuit. The power consumption in this

circuit would work out to:

$$P = EI = 10 \times .25 = 2.5$$

watts

In some circumstances it may be convenient to combine the power formula with Ohm's Law. For instance, let's say we know the current and resistance, and we need to know the power, but we're not too concerned about the voltage. Ohm's law allows us to derive the voltage from the current and the resistance:

$$E = IR$$

We can substitute this formula for the value of E in the power equation:

$$P = EI = I \times R \times I = I^2 R$$

The power equals the current squared, multiplied by the resistance. Similarly, we can find the power from the voltage and the resistance, without knowing the current:

$$I = E/R$$

$$P = EI = E \times (E/R) = E^2/R$$

#### **COMBINING COMPONENT VALUES**

Most practical electronics circuits are fairly complex, including several different resistances, capacitances, and inductances. In addition, in designing a circuit an unusual component value may be required even though it is not readily available. To deal with both these situations, we need to know how to combine component values.

#### **Combining Resistances**

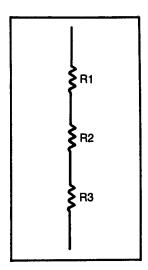

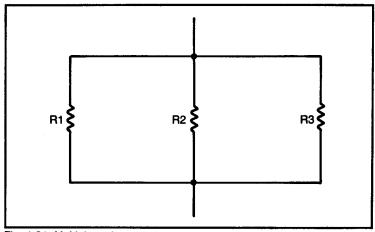

We will probably be working most frequently with multiple resistances. Multiple resistances may be combined in series, as shown in Fig. 1-23 or in parallel, as shown in Fig. 1-24.

The series combination is perfectly straightforward. The resistances are simply added together:

$$R_{t} = R1 + R2 + R3 + ... + R_{n}$$

Fig. 1-23. Resistances in series add.

For example, let's say we have the following three resistances in series:

220 ohms 100 ohms 470 ohms

The total effective resistance would be equal to:

$$R_r = 220 + 100 + 470 = 790 \text{ ohms}$$

Fig. 1-24. Multiple resistances may also be combined in parallel.

The formula for parallel resistances is not quite so obvious:

$$1/R_{t} = 1/R1 + 1/R2 + 1/R3 + ... + 1/R_{n}$$

Using the same resistance values in the preceeding example, we find the parallel combination works out to:

$$1/R_t = 1/220 + 1/100 + 1/470 = 0.0045 + 0.01 + 0.0021 = 0.0166$$

$$R_{\star} = 1/0.0166 = 60 \text{ ohms}$$

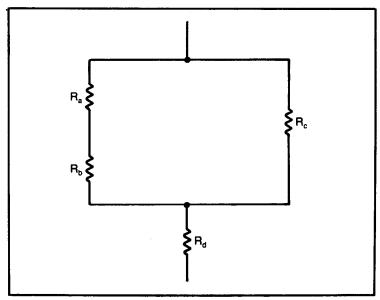

Most practical circuits include both series and parallel resistances. To combine the values, simply break up the circuit into simple series or parallel combinations in steps. A simple example is shown in Fig. 1-25. First add the series combination of  $R_a$  and  $R_b \, (R_{ab})$ , then figure the parallel combination of  $R_{ab}$  and  $R_c \, (R_{abc})$ . Finally, take the series combination of  $R_{abc}$  and  $R_d$ .

The series combination will always result in a total greater than any of the individual resistances making up the combination. A parallel combination always leads to a smaller total resistance than any of the individual resistances making up the combination.

Fig. 1-25. In practical circuits we usually find both series and parallel resistances.

## **Combining Capacitances**

Capacitances are combined in just the opposite way as resistances. For series combinations of capacitances, use this formula:

$$1/C_{+} = 1/C1 + 1/C2 + 1/C3 + ... + 1/C_{n}$$

Or, when there are just two capacitances in series:

$$C_t = (C1 \times C2)/(C1 + C2)$$

Capacitances in parallel simply add:

$$C_{r} = C1 + C2 + C3 + ... + C_{n}$$

## **Combining Inductances**

Inductances don't figure too prominently into the types of circuits we will be discussing in this book, but it is worth mentioning that they combine in exactly the same way as resistances. That is, for series combinations:

$$L_{t} = L1 + L2 + L3 + ... + L_{n}$$

And, for parallel combinations:

$$1/L_{t} = 1/L1 + 1/L2 + 1/L3 + ... + 1/L_{n}$$

Or:

$$L_{\star} = (L1 \times L2)/(L1 + L2)$$

### **KIRCHHOFF'S LAWS**

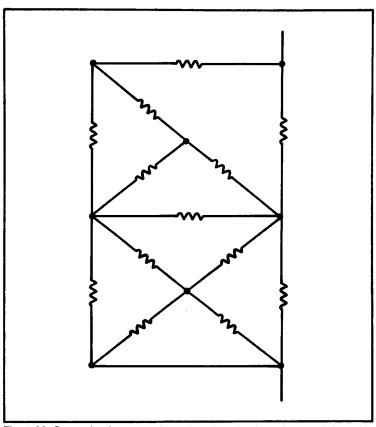

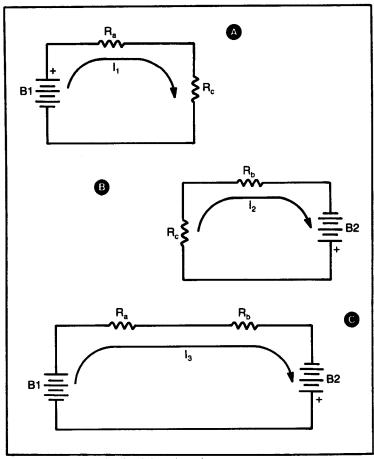

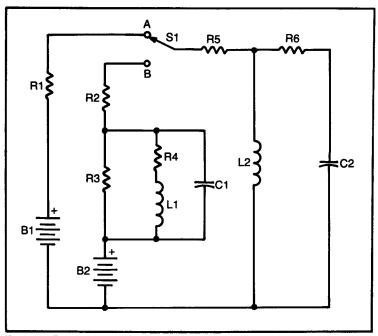

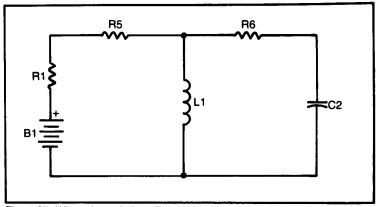

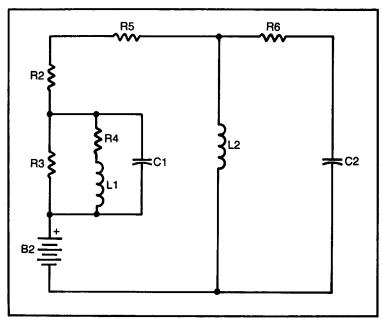

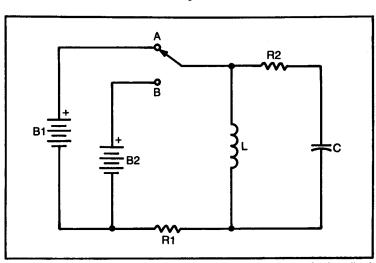

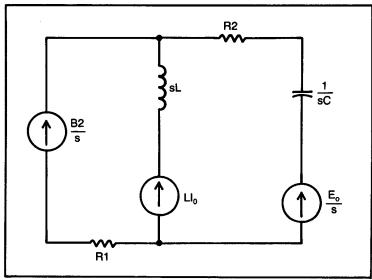

Some circuits, like the one shown in Fig. 1-26, can't be reduced to convenient series and parallel combinations. Kirchhoff's laws are a set of handy tools for analyzing complex electronics circuits.

# Kirchhoff's Voltage Law

Kirchhoff's voltage law is based on the concept of the loop. A loop is simply any closed conducting path. It may include voltage

Fig. 1-26. Some circuits cannot be reduced to simple series-parallel combinations.

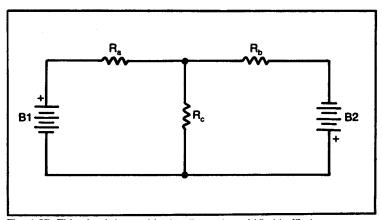

Fig. 1-27. This circuit is used in the discussion of Kirchhoff's laws.

sources (but not current sources), resistances, reactances, and conductors in any series combination. The circuit shown in Fig 1-27 has three loops, which are illustrated separately in Fig. 1-28. We only need to look at two of these to fully analyze the circuit. When using Kirchhoff's voltage law, you use the minimum number of loops that contain all of the circuit elements. Often there are several possibilities, and it doesn't matter which you use—you'll get the same results. Therefore, it makes sense to select the loops that will be the easiest to work with.

In Fig. 1-28 the loop currents are shown. A loop current is assumed to flow only within its associated loop. It is a mathematical fiction, which may or may not correspond to the real current actu-

Fig. 1-28. The sample circuit has three loops.

ally flowing through that portion of the circuit. The loop current is assumed for mathematical convenience. The equations will work out and ultimately give us the correct results, and that's what matters.

Simply put, Kirchhoff's voltage law states that the algebraic sum of all voltage sources in any loop is equal to the algebraic sum of the voltage drops around the loop. The entire voltage is dropped within the loop. The voltage drops are considered to be caused not just by the loop's current, but by any other loop current flowing through the resistance element in question.

Select a direction (either clockwise or counterclockwise) for each loop current. It doesn't matter whether this relates to the direction of the actual current flow or not. If the "wrong" choice is made, the results will be negative rather than positive. The numerical values will be the same in either case.

It usually is simplest if all loop currents are assumed to flow in the same direction. I have arbitrarily selected a clockwise direction as a standard in the following examples.

The sign of the current flow through a resistance element determines the polarity of the voltage drop across that element. If the current through a resistance element is in the same direction as the loop current, the voltage drop is positive, otherwise, it is negative. Of course, voltage drops due to the loop current will always be positive, by definition. Voltage drops due to external loop currents may be either positive or negative.

If the loop current flows through a voltage source from the negative terminal to the positive terminal, the voltage is given a positive value, otherwise, it is negative.

Let's put Kirchhoff's voltage law to work analyzing the circuit shown in Fig. 1-27. Loops A and B in Fig. 1-28 contain all of the circuit elements, so they will be sufficient for our analysis. We can ignore loop C.

For our example, we will assume the following values for the circuit elements:

B1 = 9 volts B2 = 12 volts  $R_a = 10 \text{ ohms}$   $R_b = 50 \text{ ohms}$   $R_a = 20 \text{ ohms}$

The circuit is redrawn in Fig. 1-29 with the two loop currents shown.

Fig. 1-29. The circuit is redrawn here for convenience, with two loop currents shown.

In loop A we have one voltage source (B1), and two resistance elements ( $R_a$  and  $R_c$ ). Only loop current  $I_1$  flows through  $R_a$ , so the voltage drop across this component is simply:

$$E_a = I_1 \times R_a$$

However, two loop currents ( $I_1$  and  $I_2$ ) flow through  $R_c$ . Since  $I_c$  is flowing in the opposite direction as  $I_1$ , it is given a negative value. The total voltage drop across this resistance element becomes:

$$\mathbf{E}_{c} = (\mathbf{I}_{1} \times \mathbf{R}_{c}) - (\mathbf{I}_{2} \times \mathbf{R}_{c})$$

According to Kirchhoff's voltage law, the sum of all voltage sources in the loop must be equal to the sum of all voltage drops in the loop. Therefore:

$$B1 = E_a + E_c$$

=  $(I_1 \times R_a) + (I_1 \times R_c) - (I_2 \times R_c)$

=  $I_1 \times (R_a + R_c) - (I_2 \times R_c)$

Plugging in the values from our parts list, we find:

$$g = I_1 \times (10 + 20) - (I_2 \times 20)$$

=  $(I_1 \times 30) - (I_2 \times 20)$

We can do the same thing with loop B:

$$B2 = (I_2 \times R_b) + (I_2 \times R_c) - (I_1 \times R_c)$$

$$= I_2 \times (R_b + R_c) - (I_1 \times R_c)$$

$$I_2 = I_2 \times (50 + 20) - (I_1 \times 20)$$

$$= (I_2 \times 70) - (I_1 \times 20)$$

We now have a pair of simultaneous equations with two variables:

$$g = (I_1 \times 30) - (I_2 \times 20)$$

$I_2 = (I_2 \times 70) - (I_1 \times 20)$

There are several methods for solving simultaneous equations. This is probably the simplest approach. First, rearrange one of the equations, as if solving for one of the variables. We will modify the second equation to give a formula for I<sub>2</sub>:

$$I_2 = (I_2 \times 70) - (I_1 \times 20)$$

$I_2 + (I_1 \times 20) = I_2 \times 70$

$I_2 = [I_2 + (I_1 \times 20)]/70$

Now, we can substitute this formula for  $\mathbf{I}_2$  in the first equation:

$$\begin{array}{lll} \mathbf{g} &=& (\mathbf{I}_1 \times 30) - (\mathbf{I}_2 \times 20) \\ &=& (\mathbf{I}_1 \times 30) - \{[(\mathbf{I}_2 + (\mathbf{I}_1 \times 20)]/70\} \times 20) \\ &=& (\mathbf{I}_1 \times 30) - \{[(\mathbf{I}_2 \times 20) + (\mathbf{I}_1 \times 20 \times 20)]/70\} \\ &=& (\mathbf{I}_1 \times 30) - \{(240/70) + [(\mathbf{I}_1 \times 400)/70]\} \\ &=& (\mathbf{I}_1 \times 30) - [3.43 + (\mathbf{I}_1 \times 5.71)] \\ &=& (\mathbf{I}_1 \times 30) - (\mathbf{I}_1 \times 5.71) - 3.43 \\ &=& [\mathbf{I}_1 \times (30 - 5.71)] - 3.43 \\ &=& (\mathbf{I}_1 \times 24.29) - 3.43 = 9 \end{array}$$

Because we have only one unknown variable in this equation now, we can rearrange the equation to solve for the unknown value:

$$9 = (I_1 \times 24.29) - 3.43$$

$9 + 3.43 = I_1 \times 24.29$

$12.43/24.29 = I_1$

$0.51 = I_1$

Loop current  $I_1$  equals approximately 0.51 amp.

Now that we know the value of  $I_1$  we can use our modified formula to solve for  $I_2$ :

$$I_2 = [I_2 + (I_1 \times 20)]/70$$

$$= [I_2 + (0.51 \times 20)]/70$$

$$= (I_2 + 10.24)/70$$

$$= 22.24/70$$

$$= 0.32 \text{ amp}$$

The next step is to use these current values to find the actual voltage drops across each of the resistance elements.

Resistor R<sub>a</sub> is affected only by current I<sub>1</sub>, so:

$$E_a = I_1 \times R_a$$

$$0.51 \times 10 = 5.1 \text{ volts}$$

Resistor R<sub>c</sub>, however, is affected by both the loop currents, so the voltage drop is slightly more complex:

$$E_c = (I_1 \times R_c) - (I_2 \times R_c)$$

=  $(0.51 \times 20) - (0.32 - 20)$

=  $10.2 - 6.4 = 3.8 \text{ volts}$

Finally,  $R_b$  is affected only by loop current  $I_2$ , so its voltage drop works out to:

$$E_b = I_2 \times R_b$$

= 0.32 \times 50 = 16 volts

Wait a minute! How can more voltage be dropped than exists in the loop? Loop B contains only B2, which puts out 12 volts. The answer lies in our sign conventions.  $I_1$  runs counter to  $I_2$ . So, for loop B, the voltage drop across  $R_c$  is:

$$E_{c2} = (I_2 \times R_c) - (I_1 \times R_c)$$

=  $(0.32 \times 20) - (0.51 \times 20)$

=  $6.4 - 10.2 = -3.8 \text{ volts}$

B1 should equal the sum of the voltage drops in loop A ( $E_a$  and  $E_c$ ) and B2 should equal the sum of the voltage drops in loop B ( $E_b$  and  $E_{c2}$ ):

B1 = 9 =

$$E_a$$

+  $E_c$  = 5.1 + 3.8 = 8.9 volts

B2 =  $I_2$  =  $E_b$  +  $E_{c2}$  = 16 - 3.8 = 12.2 volts

The slight differences here are due to cumulative roundoff errors in the calculations. Our results are close enough for most practical purposes.

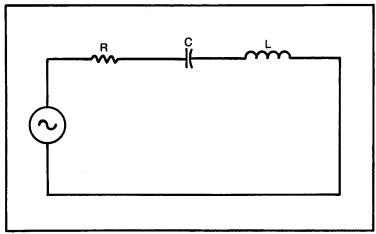

#### Kirchhoff's Current Law

Besides his voltage law, Kirchhoff also came up with a law for analyzing currents in complex circuits. Remember that the loop currents we dealt with in Kirchhoff's voltage law were mathematical fictions, which may or may not correspond to the actual current flowing through the components. To deal with actual currents, rather than the mathematical fictions of Kirchhoff's voltage law, we use Kirchhoff's current law.

Again, we have to start off with a simple definition. A node is a connection point between two or more conductors. The nodes in our sample circuit are indicated in Fig. 1-30.

According to Kirchhoff's current law, the amount of current flowing into a node always exactly equals the current flowing out of that node. In other words, the algebraic sum of all currents through a node is zero. Current flowing into a node is assumed to be positive. Current flowing out of a node is assumed to be negative.

Fig. 1-30. For Kirchhoff's current law, circuit nodes are identified.

For voltage drops across resistance elements, the terminal where the current enters is assumed to be at a higher potential than the terminal where the current exits.

If a circuit has N nodes, we will need to examine N-1 nodes to completely analyze the circuit. In our sample circuit of Fig. 1-30, we only have two nodes, so we only need one to solve the circuit. We will use node A. There are three current paths into node A. These are marked in the diagram as  $\mathbf{I}_1$ ,  $\mathbf{I}_2$ , and  $\mathbf{I}_3$ . According to Kirchhoff's current law, the algebraic sum of these currents must be equal to zero. That is:

$$I_1 + I_2 + I_3 = 0$$

Current  $I_1$  flows through resistor  $R_a$ . It is obviously equal to the voltage drop across  $R_a$ , divided by its resistance (Ohm's law-I = E/R).

Now, the voltage drop across  $R_a$  must be equal to the voltage going into the resistance element at the positive terminal (which is B1 in this case) minus the voltage at the negative terminal of the resistance element, which we will call  $E_a$ . The current direction of  $I_2$  means node A is less positive (more negative) than node B, so voltage  $E_a$  takes on a negative sign. Putting this all together, we can create an Ohm's law equation for current  $I_1$ :

$$I_1 = [B1 - (-E_a)]/R_a$$

The two negative signs in front of E<sub>a</sub> cancel out, leaving:

$$I_1 = (B1 + E_a)/R_a$$

Current  $I_2$  is defined by the voltage drop across  $R_c$ . This is simply equal to  $E_a$ , so:

$$I_2 = E_2/R_c$$

Finally,  $I_3$  is determined by the voltage drop across  $R_b$ . The input voltage is B2, and the output voltage is  $E_a$ . B2 is negative because of the battery polarity.  $E_a$  is negative because of the direction of the  $I_2$  current flow. This makes  $I_3$  equal to:

$$I_3 = [-B2 - (-E_a)]/R_b = (E_a - B2)/R_b$$

The next step is to substitute these formulas into the original node equation:

$$I_1 + I_2 + I_3 = 0$$

$[(B1 + E_a)/R_a] + (E_a/R_c) + [E_a - B2)/R_b] = 0$

We can simplify and rearrange the equation like this:

$$E_a \times [(1/R_a) + (1/R_b) + (1/R_c)] = (B2/R_b) - (B1/R_a)$$

Before we go any further we will need some specific component values to work with. We will use the same values we used in the Kirchhoff's voltage law example:

B1 = 9 volts B2 = 12 volts  $R_a = 10 \text{ ohms}$   $R_b = 50 \text{ ohms}$   $R_c = 20 \text{ ohms}$

Plugging these values into this equation, we find:

$$E_a \times [(1/10) + (1/50) + (1/20)] = (12/50) - (9/10)$$

$E_a \times (0.1 + 0.02 + 0.05) = 0.24 - 0.9$

$E_a = 0.17 = -0.66$

$E_a = -0.66/0.17 = -3.88 \text{ volts}$

The negative sign simply indicates that the polarity is the opposite of the one we assumed.

We can now go back and solve for each of the currents in the circuit.

$$I_1 = (B1 + E_a)/R_a = (9 - 3.88)/10$$

= 5.12/10 = 0.512 amp = 512 mA

$I_2 = E_a/R_c = -3.88/20 = -0.194$  amp = -194 mA

$I_3 = (E_a - B2)/R_b = (-3.88 - 12)/50 = -15.88/50 = -0.318$  amps = -318 mA

The negative values for  $I_2$  and  $I_3$  simply indicate that the actual direction of current flow is the opposite of that shown in Fig. 1-30.

Let's doublecheck our work by plugging the derived current value back into the node equation:

$$I_1 + I_2 + I_3 = 0$$

$0.512 + (-0.194) + (-0.318) = 0$

$0.512 - 0.194 - 0.318 = 0$

Yes. It works.

Of course, other circuits will result in different equations. The more nodes there are, the more equations you will have to work with.

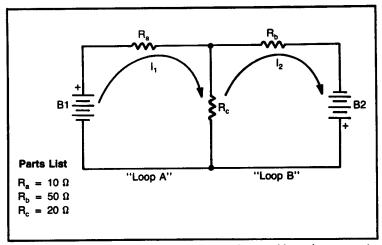

## **AC VALUES**

Formulas like Kirchhoff's laws and Ohm's law work very conveniently with dc voltages and currents. Everything is neat and straightforward. But, many electronics circuits carry ac voltages and currents. By definition, an ac signal continuously changes its value from instant to instant. How can we deal with constantly fluctuating parameters? What numbers can we plug into our equations?

There are several different methods of measuring ac signals. All are useful in some circumstances. The most straightforward approach is to simply identify the maximum level the signal reaches during each cycle. In the sine wave shown in Fig. 1-31, the *peak value* is 10 volts. Unfortunately, the peak value doesn't help us much in the circuit equations we are dealing with in this chapter. The actual voltage is 10 volts for only a small portion of each cycle. Usually the actual voltage will be lower than the peak value.

Closely related to the peak value is the *peak-to-peak value*. This is nothing more than the measurement of the distance from the positive peak to the negative peak. In our sample sine wave, the peak-to-peak value is 20 volts (+10 volts to -10 volts). For sine waves, the peak-to-peak value will always be twice the peak value.

An obvious solution would be to calculate the average value of the ac signal. To do this, you use only half the cycle (either positive or negative, it doesn't matter). If the entire cycle is used, the mathematical average will always work out to zero because the two opposite half-cycles will cancel each other out. For sine waves, the average value will be equal to:

Average =

$$0.636 \times Peak$$

This equation is not valid for other waveshapes.

Fig. 1-31. Even a simple sine wave can be measured in several different ways.

The average value gives us a better idea of the ac parameters. Unfortunately, it cannot be used in standard circuit equations, such as Ohm's law.

What we need is a way to determine the equivalent dc value for the ac signal. This can be experimentally determined by passing the signals through a resistance element. The ac voltage that heats up the resistance element the same amount as the dc voltage is assumed to be "equal" to the dc voltage.

A complex mathematical formula can be used to calculate the equivalent value. The system is called *root-mean-square*, or RMS. Fortunately, we don't have to bother with the derivation. The RMS value of a sine wave can be calculated directly from the peak value by using this formula:

$$RMS = 0.707 \times Peak$$

The RMS value can also be found by starting with the average value, using this equation:

$$RMS = 1.11 \times Average$$

Remember that these equations are valid for sine waves only.

RMS values can be plugged directly into Ohm's law, Kirchhoff's laws, and other dc formulas, and will give the correct results.

Here is a summary of the basic ac values and their relationships:

$RMS = 0.707 \times Peak$   $RMS = 1.11 \times Average$  $Average = 0.9 \times RMS$

Average =  $0.636 \times Peak$

Peak =  $1.41 \times RMS$

Peak =  $1.57 \times Average$

Peak-to-Peak =  $2 \times Peak$

These equations are for sine waves only. They will not give correct results for other waveforms. Fortunately, for the circuit designer sine waves are by far the norm.

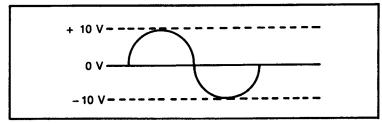

### RESISTANCE IN AC CIRCUITS

Ac resistance is even more complex, because it is made up of several components:

☐ Resistance☐ Capacitive Reactance☐ Inductive Reactance

The resistance component is the same as dc resistance. It is a constant, and does not change with the frequency of the ac signal. The reactance components are frequency dependent. Capacitive reactance decreases with increases in frequency. It is defined as the ac resistance of a purely capacitive component. The formula is:

$$X_c = 1/(2 \pi FC)$$

Capacitive reactance is infinite at dc (0 Hz).

Inductive reactance is the ac resistance exhibited by a purely inductive component (coil). It increases with increases in frequency. The formula for inductive reactance is:

$$X_1 = 2 \pi FL$$

Practical circuits include a combination of capacitive reactance, inductive reactance, and resistance. The total ac resistance at a specific frequency is called the impedance. Remember that impedance is a frequency specific value. It will change with the applied frequency.

Capacitive and inductive reactances are, by definition, out-ofphase with each other. This means that they can not simply be added together. The formula for calculating impedance is:

$$Z = \sqrt{R^2 + (X_1 - X_c)^2}$$

where Z is the impedance, R is the dc resistance,  $X_l$  is the inductive reactance, and  $X_c$  is the capacitive reactance. All values are in ohms.

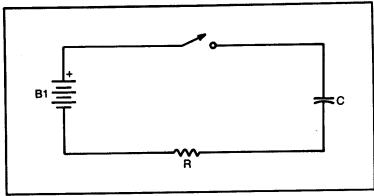

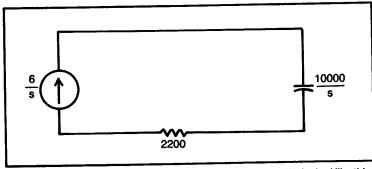

The circuit shown in Fig. 1-32 includes an ac voltage source.

Fig. 1-32. For ac resistances we have to consider capacitors, and inductors, as well as simple resistors.

a capacitor, a coil, and a resistor. For simplicity, we will assume that each of the components is theoretically perfect—that is, the capacitor is purely capacitive (no resistive or inductive elements) the resistor is purely resistive, and the coil is purely inductive. All practical components will exhibit some dc resistance and both capacitive and inductive reactance. Fortunately, in most cases the leakage values (resistance and inductance in a capacitor, for instance) are usually so small they don't have any noticeable effect on the circuit's operation, so they may be reasonably ignored.

For our sample problems, we will assume the following component values:

| Ac voltage | 120 volts                   |

|------------|-----------------------------|

| R          | 2700 ohms (2.7 k $\Omega$ ) |

| С          | 0.22 μF (0.00000022 farad)  |

| L          | 150 mH (0.15 henry)         |

We can't perform any of the calculations without knowing the signal frequency. We will start by assuming that it is 60 Hz. This makes the capacitive reactance equal to:

$$X_c = 1/(6.28 \text{ FC})$$

= 1/(6.28 × 60 × 0.00000022)

= 1/0.0000829

= 12057 ohms

For convenience, we can round this off to 12,000 ohms, or  $12 \text{ k}\Omega$ . At the same time, the inductive reactance works out to about:

$$X_1 = 6.28 \text{ FL}$$

= 6.28 × 60 × 0.15

= 56 ohms

The dc resistance, of course, is unaffected by the signal frequency. It is a constant 2700 ohms.

Combining the three resistive values (R,  $X_c$ , and  $X_i$ ) we get a total impedance of:

$$Z = \sqrt{R^2 + (X_1 - X_c)^2}$$

$$= \sqrt{2700^2 + (56 - 12057)^2}$$

$$= \sqrt{7290000 + (-12001)^2}$$

$$= \sqrt{7290000 + 144024000}$$

$$= \sqrt{151314000}$$

$$= 12301 \text{ ohms}$$

at 60 Hz.

Finally, we can now use Ohm's law to find out how much current is flowing through this circuit at 60 Hz:

$$I = E/Z = 120/12301 = 0.0098 \text{ amp} = 9.8 \text{ mA}$$

Next, let's see what happens when we increase the signal frequency to 250 Hz:

$$X_c = 1/(6.28 \times 250 \times 0.00000022)$$

= 1/0.0003456

= 2894 ohms

$X_l = 6.28 \times 250 \times 0.15 = 236 \text{ ohms}$

$Z = \sqrt{2700^2 + (236 - 2894)^2}$

=  $\sqrt{7290000 + 2364^2}$

=  $\sqrt{7290000 + 7065532}$

=  $\sqrt{1435532}$

= 3789 ohms

$I = 120/3789 = 0.0317 = 31.7 \text{ mA}$

Now we will increase the signal frequency to 1000 Hz. (We won't bother to show the intermediate steps of the calculations):

$X_c = 723 \text{ ohms}$   $X_1 = 942 \text{ ohms}$  Z = 2709 ohmsI = 0.0443 amp = 44.3 mA

One last example. This time the signal frequency is 5000 Hz:

$X_c = 145 \text{ ohms}$   $X_1 = 4172 \text{ ohms}$  Z = 5306 ohmsI = 0.0226 amp = 22.6 mA

Notice how the impedance in this circuit starts out high (low current), then decreases as the signal frequency increases (current flow increases), until a certain point is passed, then the impedance starts to increase (and current flow decreases) as the signal frequency is further increased. The crossover point is of considerable significance. It is called resonance.

## Series Resonance

Because the capacitive reactance decreases as the signal frequency increases, and the inductive reactance increases with the signal frequency, at some specific frequency the capacitive reactance will be exactly equal to the inductive reactance. Something very interesting happens at this frequency:

$$Z = \sqrt{R^2 + (X_1 - X_c)^2} = \sqrt{R^2 + (0)^2}$$

$$= \sqrt{R^2 + 0} = \sqrt{R^2} = R = Z$$

The capacitive and inductive reactances cancel each other out. The ac impedance simply equals the dc resistance. If you think about it for a minute, it becomes clear that this is the minimum value the impedance of the circuit can ever have.

The condition when the capacitive reactance equals the inductive reactance is called resonance. The frequency where this occurs is called the resonant frequency. There is always one (and only one) resonant frequency for any capacitance/inductance series combination.

At resonance, a capacitance and an inductance in series exhibit their minimum impedance. At frequencies above or below resonance, the impedance will be greater. The further away from the resonant frequency the signal frequency is (in either direction) the higher the circuit impedance.

The resonant frequency for any capacitance/inductance combination can be found with this formula:

$$F = 1/(2 \pi \sqrt{LC})$$

where F is the frequency in hertz, L is the inductance in henries, and C is the capacitance in farads. Of course, 2  $\pi$  is about 6.28.

Let's find the resonant frequency for the sample circuit we have been using for the last few pages. Remember, C = 0.00000022 and L = 0.15:

F =

$$1/(6.28 \times \sqrt{(0.15 \times 0.00000022)})$$

=  $1/(6.28 \times \sqrt{0.0000000033})$

=  $1/(6.28 \times 0.001817)$

=  $1/0.0011414$

=  $876$  Hz.

The resonant frequency formula can be rearranged to solve for either of the component values. Notice that the dc resistance has absolutely no effect on the resonant frequency.

Let's say, for example, we need a circuit that is resonant at 1000 Hz. We will keep our 150 mH coil. What value should we change the capacitor to for the required resonant frequency? First, we rearrange the equation, which becomes:

$$C = 1/(4 \pi^2 F^2 L)$$

$4 \pi^2$  equals approximately 39.48, so the equation may be simplified to:

$$C = 1/(39.48 F^2L)$$

Plugging in the values for our sample problem, we find we need a capacitance of about:

$$C = 1/(39.48 \times (1000)^2 \times 0.15)$$

= 1/ (39.48 \times 1000000 \times 0.15)

= 1/5921762.6

= 0.000000169 farad

$= 0.169 \mu F$

Similarly, the resonance equation may also be rearranged to solve for the inductance value:

$$L = 1/(39.48 F^2C)$$

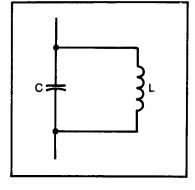

#### Parallel Resonance

So far we have been dealing solely with circuits in which the capacitive element and the inductive element are in series, as shown in Fig. 1-32. But they may also be connected in parallel, as illustrated in Fig. 1-33. This change has a number of effects. For one thing, the impedance equation becomes somewhat more complex:

$$Z = \sqrt{R^2 + [(X_1 \times X_c)/(X_1 - X_c)]^2}$$

To study the effects of this, we will use the same values from our previous example problems:

Ac voltage = 120 volts

R = 2700 ohms

$C = 0.22 \mu F (0.00000022 farad)$

L = 150 mH (0.15 henry)

There is no need to repeat the reactance calculations for individual frequencies, since they are exactly the same as before:

$$60 \text{ Hz} \qquad X_c = 12057 \qquad X_l = 56$$

Fig. 1-33. In a parallel resonant circuit, the ac resistance is theoretically infinite at resonance.

The impedance at 60 Hz is therefore equal to:

$$Z = \sqrt{2700^2 + [(56 \times 12057)/(56 - 12057)]^2}$$

$$= \sqrt{7290000 + (675192/ - 12001)^2}$$

$$= \sqrt{7290000 + (-56.26)^2}$$

$$= \sqrt{7293165.3352}$$

$$= 2700.5861 \text{ ohms}$$

Skipping the intermediate steps of the calculation, we find that raising the signal frequency to 250 Hz changes the impedance to:

$$Z = 2712.2 \text{ ohms}$$

Now, if the signal frequency is 1000 Hz, the impedance works out to:

$$Z = 4118.42 \text{ ohms}$$

Finally, when the signal frequency is raised to 5000 Hz the impedance becomes:

$$Z = 2704.1415$$

Notice that as the frequency increases, the impedance increases, until a specific point is reached. Then the impedance starts to decrease with increasing frequency. Once again, the crossover point is the resonant frequency. The resonant frequency is the same for a parallel circuit as for a series circuit, assuming the same components are used in both. The calculations are exactly the same in either case. The only difference is in the behavior of the circuit as the resonant frequency.

We've already determined that resonant frequency for this particular combination of components is 876 Hz when the capacitive reactance and the inductive reactance each equal approximately 826 ohms. Let's see what happens to the impedance in this case:

$$Z = \sqrt{\frac{2700^2 + [(826 \times 826)/(826 - 826)]^2}{7290000 + (682276/0)^2}}$$

$$= \sqrt{7290000 + \infty}$$

$$Z = \infty$$

In a parallel circuit, the impedance is theoretically infinite at resonance.

To summarize: in a series circuit, the impedance is at its minimum value (R) at resonance, and in a parallel circuit, the impedance is at its maximum value  $(\infty)$  at resonance.

### TRIGONOMETRIC FUNCTIONS

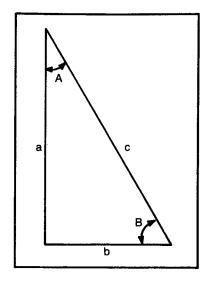

Many electronics calculations require basic trigonometric functions. Essentially, trigonometry is nothing more than a set of rules for defining relationships between angles and side lengths in triangles. A triangle has only three sides and angles, so only a limited number of combinations are possible.

We are primarily concerned with right triangles, which have one 90° (right) angle. A typical right triangle is shown in Fig. 1-34. The longest side (c) is called the hypotenuse. It is always directly opposite the right angle. The length of the sides of a right triangle always bear a specific mathematical relationship:

$$C^2 = a^2 + b^2$$

This is true for all right triangles.

Fig. 1-34. Trigonometric functions are defined as the relationships between various angles and side lengths of a right triangle.

Similarly, there are six basic relationships between the angles and the side lengths. Each is given a specific name, as follows:

sine cosine tangent arctangent secant cosecant

For angle A in Fig. 1-34, we can find the values for each of these relationships:

sine A = b/c cosine A = a/c tangent A = b/a arctangent A = a/b secant A = c/a cosecant A = c/b

The same relationships hold true for angle B, except that sides a and b are reversed:

sine A = a/c

cosine A = b/c

tangent A = a/b

arctangent A = b/a

secant A = c/b

cosecant A = c/a

Notice that the B angle can be figured from A, because of the following relationships:

sine B = cosine A

cosine B = sine A

tangent B = arctangent A

arctangent B = tangent A

secant B = cosecant A

cosecant B = secant A

In most practical electronics work, we will be working from the angle, not side lengths of a hypothetical right triangle. There are mathematical equations for solving the trig functions of an angle, but they are long and complicated. Generally, it is more practical to just use a standard trig table. A table of natural sines from 0 to 90 is given in Table 1-1. Table 1-2 lists cosines, and Table 1-3 lists tangents. These three functions are by far the most commonly encountered in electronics work. Arctangents, secants, and cosecants are rarely used.

Most scientific calculators and computers also include trigonometric functions, so there won't be many occasions when the circuit designer will have to perform these calculations for himself. Usually a table, calculator, or computer will be available to do the work.

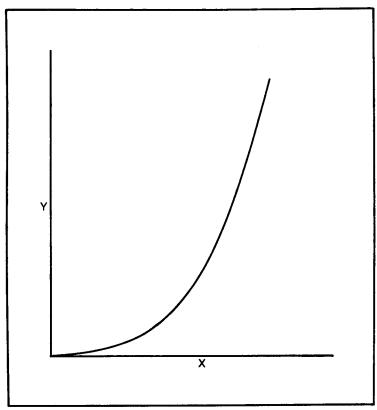

### **LOGARITHMS**

Some functions vary smoothly and evenly, giving us a nice straight line when we try to graph them. Others tend to have many values jammed together in one part of the scale, while other parts of the scale have values that are widely spaced, as shown in Fig.

Table 1-1. Table of Natural Sines.

| 0—0.0000 25—0.4226 50—0.7660 75—0.9659 1—0.0175 26—0.4384 51—0.7771 76—0.9703 2—0.0349 27—0.4540 52—0.7880 77—0.9744 3—0.0523 28—0.4695 53—0.7986 78—0.9781 4—0.0698 29—0.4848 54—0.8090 79—0.9816 5—0.0872 30—0.5000 55—0.8192 80—0.9848 6—0.1045 31—0.5150 56—0.8290 81—0.9877 7—0.1219 32—0.5299 57—0.8387 82—0.9903 8—0.1392 33—0.5446 58—0.8480 83—0.9925 9—0.1564 34—0.5592 59—0.8572 84—0.9945 10—0.1736 35—0.5736 60—0.8660 85—0.9962 11—0.1908 36—0.5878 61—0.8746 86—0.9976 |                                                                                                                                                                                                |                                                                                                                                                                                                 |                                                                                                                                                                                                 |                                                                                                                   | _ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---|

| 10 0:1100 00 0:0100 00 0:0000                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1—0.0175<br>2—0.0349<br>3—0.0523<br>4—0.0698<br>5—0.0872<br>6—0.1045<br>7—0.1219<br>8—0.1392<br>9—0.1564                                                                                       | 26—0.4384<br>27—0.4540<br>28—0.4695<br>29—0.4848<br>30—0.5000<br>31—0.5150<br>32—0.5299<br>33—0.5446<br>34—0.5592                                                                               | 51—0.7771<br>52—0.7880<br>53—0.7986<br>54—0.8090<br>55—0.8192<br>56—0.8290<br>57—0.8387<br>58—0.8480<br>59—0.8572                                                                               | 76—0.9703<br>77—0.9744<br>78—0.9781<br>79—0.9816<br>80—0.9848<br>81—0.9877<br>82—0.9903<br>83—0.9925<br>84—0.9945 |   |

| 12—0.2079 37—0.6018 62—0.8829 87—0.9986<br>13—0.2250 38—0.6157 63—0.8910 88—0.9994<br>14—0.2419 39—0.6293 64—0.8988 89—0.998<br>15—0.2588 40—0.6428 65—0.9063 90—1.000<br>16—0.2756 41—0.6561 66—0.9135<br>17—0.2924 42—0.6691 67—0.9205<br>18—0.3090 43—0.6820 68—0.9272<br>19—0.3256 44—0.6947 69—0.9336<br>20—0.3420 45—0.7071 70—0.9397<br>21—0.3584 46—0.7193 71—0.9455<br>22—0.3746 47—0.7314 72—0.9511<br>23—0.3907 48—0.7431 73—0.9563<br>24—0.4067 49—0.7547 74—0.9613       | 9—0.1564<br>10—0.1736<br>11—0.1908<br>12—0.2079<br>13—0.2250<br>14—0.2419<br>15—0.2588<br>16—0.2756<br>17—0.2924<br>18—0.3090<br>19—0.3256<br>20—0.3420<br>21—0.3584<br>22—0.3746<br>23—0.3907 | 34—0.5592<br>35—0.5736<br>36—0.5878<br>37—0.6018<br>38—0.6157<br>39—0.6293<br>40—0.6428<br>41—0.6561<br>42—0.6691<br>43—0.6820<br>44—0.6947<br>45—0.7071<br>46—0.7193<br>47—0.7314<br>48—0.7431 | 59—0.8572<br>60—0.8660<br>61—0.8746<br>62—0.8829<br>63—0.8910<br>64—0.8988<br>65—0.9063<br>66—0.9135<br>67—0.9205<br>68—0.9272<br>69—0.9336<br>70—0.9397<br>71—0.9455<br>72—0.9511<br>73—0.9563 | 84—0.9945<br>85—0.9962<br>86—0.9976<br>87—0.9986<br>88—0.9994<br>89—0.998                                         |   |

Table 1-2. Table of Cosines.

| 0—1.0000  | 25-0.9063 | 50-0.6428 | 75—0.2588 |

|-----------|-----------|-----------|-----------|

| 10.9998   | 26-0.8988 | 51—0.6293 | 76—0.2419 |

| 2-0.9994  | 270.8910  | 520.6157  | 77—0.2250 |

| 3-0.9986  | 280.8829  | 530.6018  | 780.2079  |

| 40.9976   | 29-0.8746 | 540.5878  | 790.1908  |

| 50.9962   | 300.8660  | 55-0.5736 | 800.1736  |

| 6-0.9945  | 31-0.8572 | 56-0.5592 | 81-0.1564 |

| 7—0.9925  | 32-0.8480 | 57-0.5446 | 82-0.1392 |

| 8-0.9903  | 33-0.8387 | 580.5299  | 83-0.1219 |

| 9—0.9877  | 34-0.8290 | 59-0.5150 | 840.1045  |

| 100.9848  | 35-0.8192 | 600.5000  | 85-0.0872 |

| 11—0.9816 | 36-0.8090 | 61-0.4848 | 86-0.0698 |

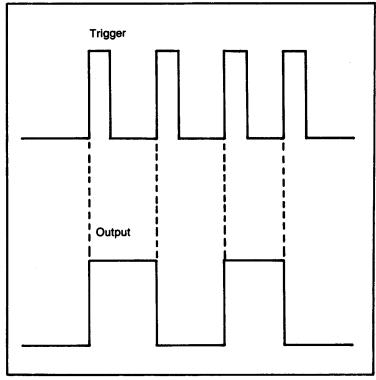

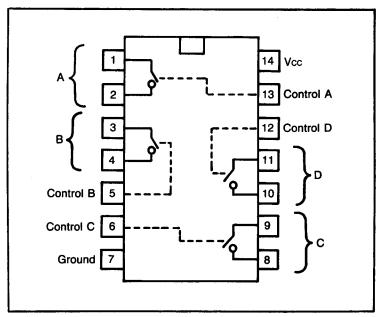

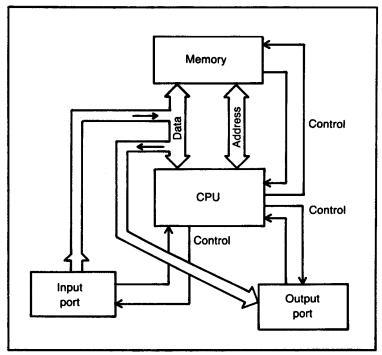

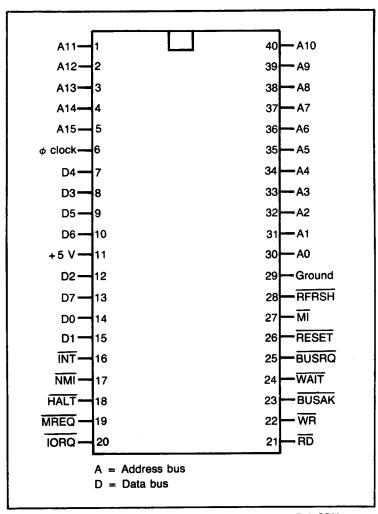

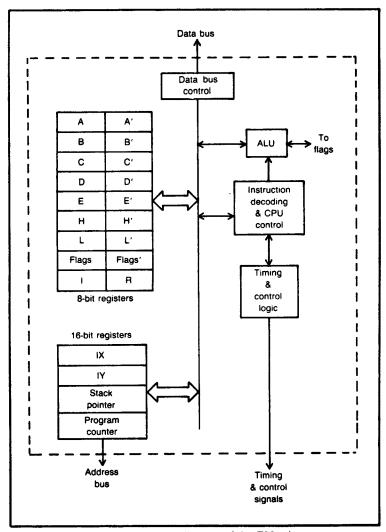

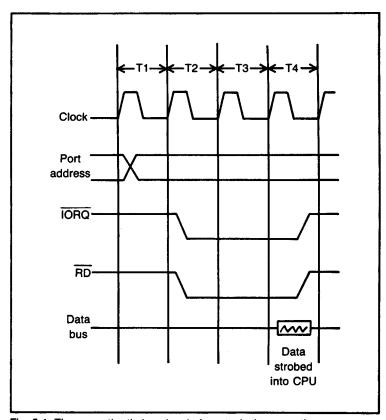

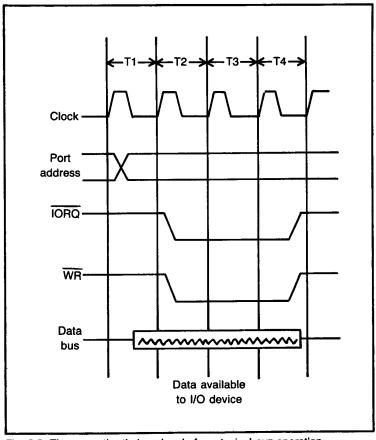

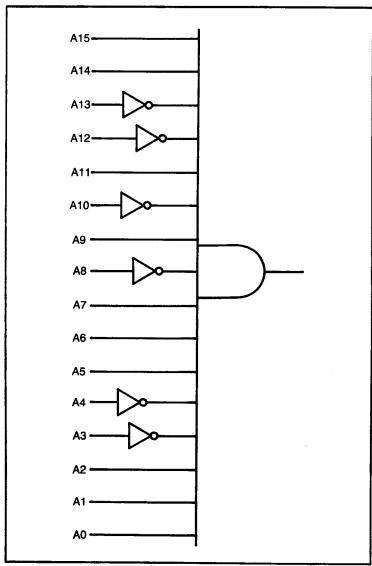

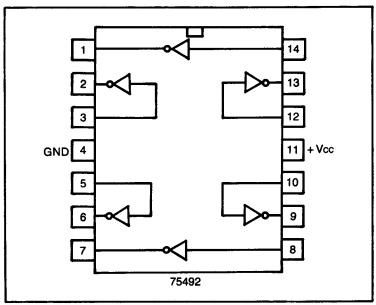

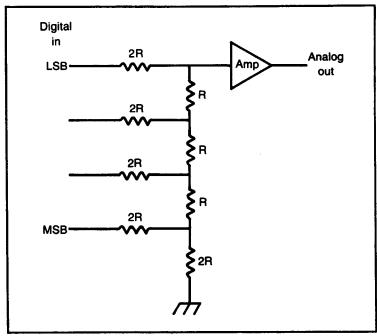

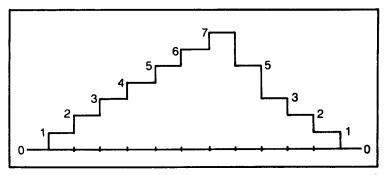

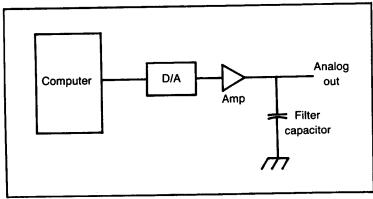

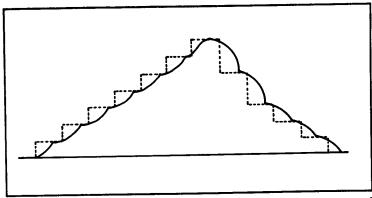

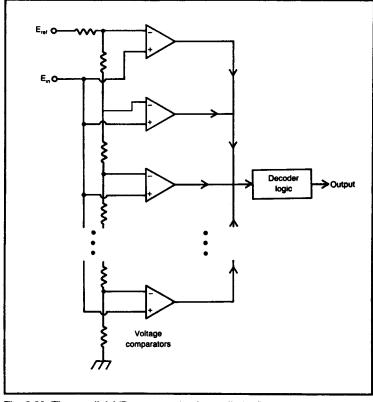

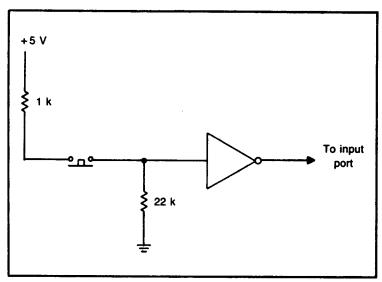

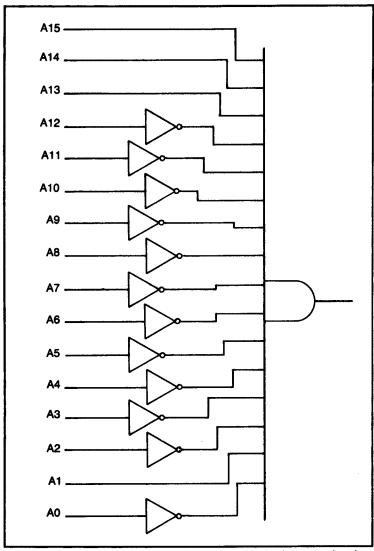

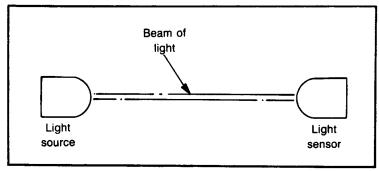

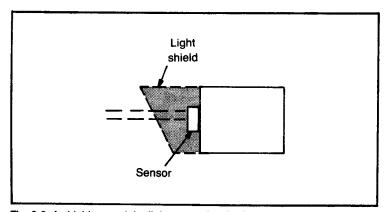

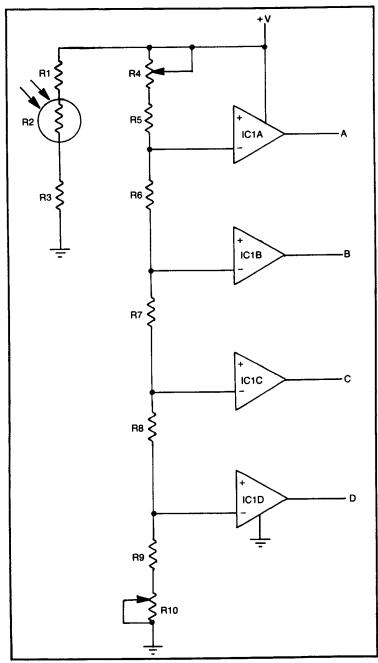

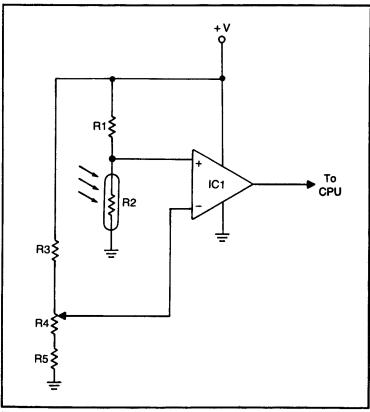

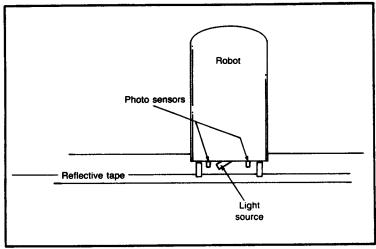

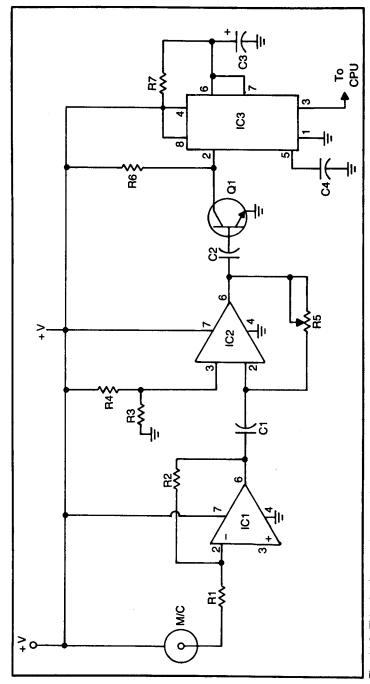

| 12-0.9781 | 370.7986  | 620.4695  | 870.0523  |